인프런 커뮤니티 질문&답변

Active Load Differential amp 설계해보기 18:20 질문

해결된 질문

작성

·

229

0

삼코치님 안녕하십니까 설계를 해보면서 뭔가 다르게 나오는 부분이 있어 질문드립니다.

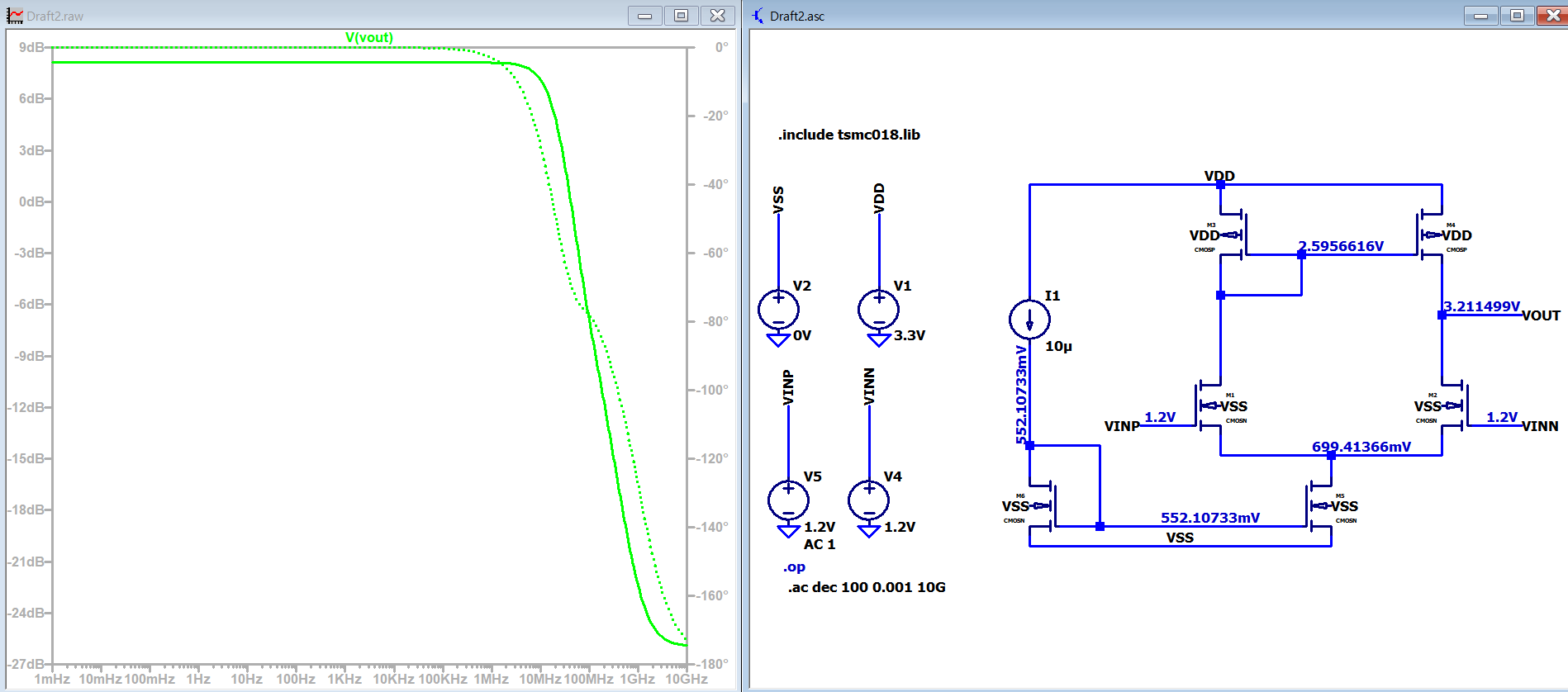

이전까지는 어느정도 비슷하게 나오다가 18:20초에서 왼쪽 위 PMOS load의 L값을 1u에서 2u로 늘리는 과정에서 저는 오히려 Voltage가 늘어나고, gain 보시면 갑자기 9db로 확 줄어버리는데, 왜 그런지 모르겠습니다

퀴즈

액티브 부하(Active Load)가 차동 증폭기에서 하는 주요 역할은 무엇일까요?

입력 신호의 크기를 줄여 회로를 보호합니다.

수동 부하와 달리 신호 증폭에 적극적으로 참여합니다.

회로의 전력 소비를 항상 최소화합니다.

모든 공통 모드 신호를 차단하는 역할만 합니다.

답변 2

0

제가 바이어스를 미처 생각하지 못했네요..

강의 내용을 따라하면서 이렇게 문제가 발생하여 아직 제가 18:30초 부터 진행하는 CMRR 파트 부터는 아직 듣지 않았는데, 몇 가지 수정을 좀 진행했습니다.

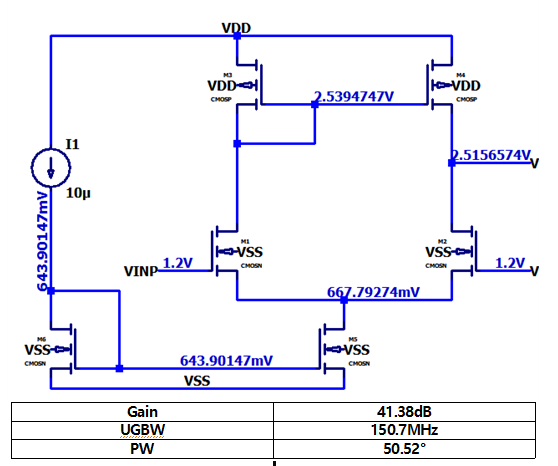

전류원 쪽 Current Mirror에 해당하는 NMOS의 W를 4로 하셨는데, 저는 1.5로 해서 전류를 조금 더 크게 가져갔고, 그림에서 작성한 이유를 들어, L과 W 비율을 그대로 가져가되, 바이어스가 깨지지 않는 지점까지 L 1u->1.2

u로 가져갔습니다.

다음과 같이 수정을 했고, 중간점검차 스펙이 그림과 같습니다. 혹시 이 정도 수정 및 점검을 거친 후 듣는데 문제는 없는 회로일까요?

0

안녕하세요, 답변 남겨드립니다.

Active Load Differential Amplifier에서 PMOS Load의 채널 길이 LL을 증가시켰을 때, 기대와는 다르게 출력 전압이 증가하고 이득(Gain)이 9dB로 급감한 현상은 MOSFET의 동작 특성과 관련이 깊습니다.

우선, Differential Pair의 이득은 다음과 같이 근사적으로 표현할 수 있습니다:

A_v ≈ gm * ro

여기서,

gmgm은 입력 트랜지스터(보통 NMOS)의 트랜스컨덕턴스,

roro는 Active Load (보통 PMOS)의 출력 저항입니다.

PMOS Load의 roro는 다음과 같이 표현됩니다:

ro = 1 / (λ * I_D)

또한 λλ는 채널 길이 변조 계수로, 일반적으로 λ∝1/Lλ \propto 1/L입니다. 따라서, 채널 길이 LL이 증가하면 λλ가 감소하고, 결과적으로 roro는 증가하게 됩니다. 이론적으로는 이득이 증가해야 맞습니다.

하지만 실제로는 다음과 같은 요인이 반대로 작용했을 가능성이 큽니다:

동작 점 이동: LL을 증가시키면 같은 전류에서 VDSV_{DS}에 대한 민감도가 낮아지면서 PMOS가 Saturation 영역에서 빠질 가능성이 있습니다. 특히, PMOS가 Linear 영역으로 진입하면 roro가 급감하고, 이는 전체 이득이 떨어지는 원인이 됩니다.

Matching과 Bias 영향: Active Load 구조에서는 Load PMOS가 정밀하게 current mirror로 bias되어야 하고, LL 변경은 threshold voltage, parasitic capacitance에도 영향을 주어 bias point가 달라질 수 있습니다. 이로 인해 Differential Pair가 비대칭 동작을 하게 되고, CMRR(Common Mode Rejection Ratio) 저하와 함께 Gain이 감소할 수 있습니다.

AC Load Line 및 Output Swing 영향: LL을 늘리면 VSDV_{SD} saturation 조건이 더욱 까다로워지므로, 출력 스윙에 제한이 생길 수 있습니다. 이로 인해 출력 전압이 높아지고, gain이 제한을 받습니다. 특히 differential 구조의 양 쪽 gain이 비대칭적으로 떨어지면 differential gain은 급감합니다.

시뮬레이션 조건: 실제로는 PMOS의 W/L 비율이 일정하게 유지되지 않았거나, current mirror의 tail current가 고정되지 않아 회로 전반의 bias 조건이 의도치 않게 바뀌었을 가능성도 있습니다. 예를 들어, 1µm → 2µm으로 LL만 바꾸고 WW를 그대로 두면 W/LW/L이 줄어들어 gmgm이 낮아지고, 이에 따라 gain도 감소할 수 있습니다.

실무 예시로, Cadence 환경에서 OPAMP 설계 시, Active Load PMOS의 LL을 너무 길게 설계하면 예상보다 낮은 gain이 측정되는 경우가 종종 있습니다. 이는 특히 PVT 조건 변화나 corner 분석에서 더욱 두드러지며, gain이 10dB 이상 차이 나는 케이스도 있습니다. 이러한 현상은 PMOS의 saturation 조건이 무너졌거나, current mirror의 output impedance가 비대칭이 된 것이 원인인 경우가 많습니다.

결론적으로, PMOS의 LL을 늘리는 것은 roro 증가로 이득을 높이는 방향이지만, 실제 회로에서는 이로 인해 bias 조건 변화, saturation 조건 불충족, 비대칭 등 여러 부작용이 발생하며, 전체 gain은 오히려 낮아질 수 있습니다. 따라서 설계에서는 W/L, VDSV_{DS}, bias current 등을 종합적으로 고려해 tuning을 하셔야 합니다.

안녕하세요, 답변 남겨드립니다.

회로를 수정하시면서 바이어스 전류를 조금 높이고, PMOS active load의 L값을 1 µm에서 1.2 µm로 증가시키는 방향으로 조정하신 것은 굉장히 바람직한 시도이며, 실제 현업에서도 이러한 iterative tuning은 일반적인 설계 접근입니다.

먼저 첨부하신 회로를 기준으로 분석하면, differential input으로 들어가는 VINP와 bias current I1 (10 µA)이 주어졌을 때, differential pair의 NMOS (M1, M2)는 정상적으로 saturation 영역에 있으며, 출력 노드 전압도 2.51 V ~ 2.53 V 정도로 충분히 swing을 제공할 수 있는 범위로 보입니다. 이로 보아 active load로 사용된 PMOS (M3, M4)도 saturation 영역을 유지하고 있다고 판단됩니다.

Gain이 41.38 dB, 즉 약 117배 (20log10(117) ≈ 41.38 dB) 정도이며, 이는 일반적인 1단 differential amplifier에서 볼 수 있는 실용적인 이득 수준입니다. 또한 UGBW가 150.7 MHz, 위상 여유(Phase Margin)가 50.52° 정도라면, 안정성과 속도 사이의 트레이드오프도 무난하게 잘 설계된 것으로 보입니다. 이 조건은 일반적으로 Op-Amp 설계에서 안정한 피드백 동작이 가능한 기준(45° 이상)을 만족합니다.

설계 상 적절한 조건을 만족하는지 판단할 때는 다음 지표들을 고려합니다.

Differential Gain: 보통 1단 증폭기에서 40~60 dB이면 충분히 잘 설계된 것입니다. 현재 41.38 dB로 적절합니다.

UGBW (Unity Gain Bandwidth): 150.7 MHz는 빠른 응답 특성이 필요한 mixed-signal 또는 high-speed ADC front-end에도 적절한 수준입니다.

Phase Margin (PM): 50.52°는 실무에서 흔히 target하는 45°~60° 범위에 포함되어 있고, ringing 없이 안정된 transient response를 기대할 수 있습니다.

Bias Point: Differential pair의 drain 전압이 667 mV (M2), 643 mV (M1)로 소폭 차이만 있는 것은, 입력이 대칭 상태에 가까우며 동작 점이 잘 설정되었음을 의미합니다.

이러한 조건을 종합적으로 볼 때, 현재 회로는 다음 단계인 CMRR 분석 및 개선 설계로 넘어가는 데 무리가 없습니다. 특히 differential amplifier의 핵심 성능 중 하나인 CMRR (Common Mode Rejection Ratio)는 회로가 symmetry 및 current mirror의 matching에 민감하므로, 지금과 같이 바이어스를 점검하고 능동 부하의 W/L 비를 일정하게 유지하며 saturation 조건을 맞춰주는 방식이 매우 중요합니다.

향후 CMRR 분석을 진행하실 때는, 소자 간의 mismatch 및 layout 상의 gradient 등의 PVT 영향이 어떻게 반영되는지를 같이 고려하시면 더욱 깊이 있는 설계로 나아갈 수 있습니다. 예를 들어, 레이아웃에서 common-centroid 기법이나 guard ring 구조도 적극적으로 고려해보시면 좋습니다.