첫 예제를 진행하는데, 교재와 결과가 달라서 문의 드립니다.

66

작성한 질문수 4

첫번째 예제 serdes_top 를 해 보고 있는데, simulation source를 만든 결과가 교재와 다르게 나오는데...

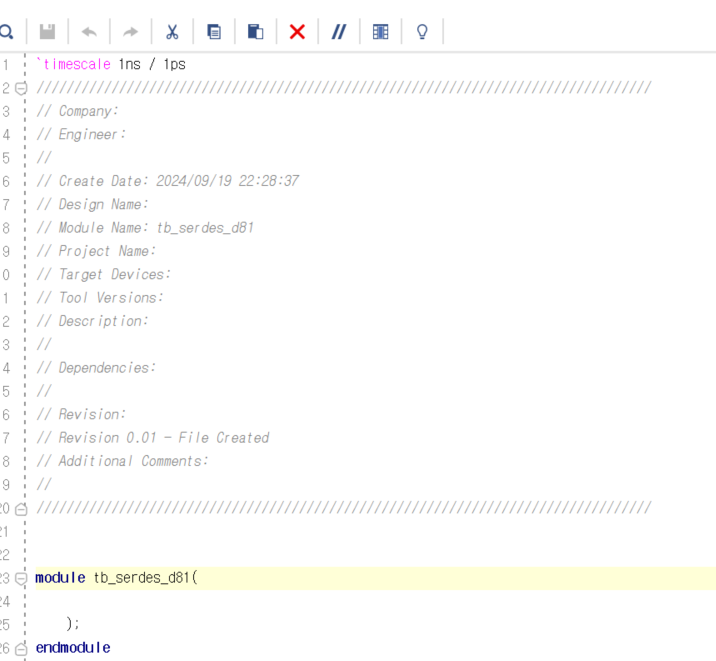

그리고 tb_serdes_d81.v 파일 내용도 교재에 있는 것과 다릅니다.

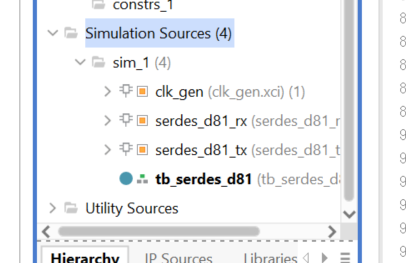

[제 결과]

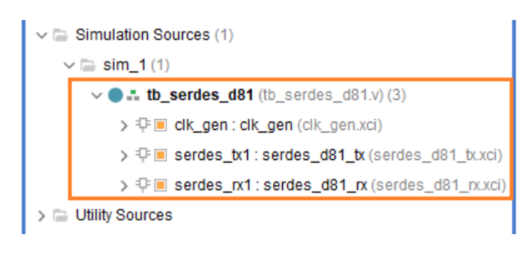

교재 결과 page 36

Page 34의 Define Module 창에서 생성된 이름 그대로 두고, I/O port 설정 하는 부분도 아무것도 추가하지 않은 그대로 두고, ok를 눌렀습니다. module definition이 변경되지 않았다는 창이 나오고, yes를 눌러 그대로 진행했습니다.

생성된 파일은 아래와 같습니다. 뭐가 잘못 되었을까요? 혹시 code를 직접 입력해야 하는 것인가요? 교재에는 그런 설명이 안 되어 있고, 자동으로 만들어 준다는 것처럼 읽히네요.

뭐가 잘못 되었을까요? 혹시 code를 직접 입력해야 하는 것인가요? 교재에는 그런 설명이 안 되어 있고, 자동으로 만들어 준다는 것처럼 읽히네요.

==> code를 입력하니, tb_serdes_d81 밑으로 clk_gen, serdes_tx1, serdes_rx1이 들어오네요.. 교재를 수정해야 할 듯 합니다. code를 파일에 직접 입력해야 한다는 한마디가 필요하네요.. Ultaedit를 사용해서 파일을 읽었다는 뜻으로만 보입니다. ㅠㅠ

답변 1

0

안녕하세요, 인프런 AI 인턴입니다.

tpxelect님, 질문 주신 내용 잘 확인했습니다. 처음 예제를 진행하시면서 교재와 실제 결과가 달라 혼란스러우셨을 것 같습니다. 설명드리겠습니다.

교재에서는 시뮬레이션 소스 파일이 자동으로 생성된다고 설명되어 있지만, 이미지로 제공된 결과와 같이 필요한 모듈들이 제대로 생성되지 않은 것 같습니다. 이를 해결하기 위해서는 코드 입력이 필요합니다.

생성된 Verilog 파일을 보면 tb_serdes_d81 모듈이 빈 상태로 정의되어 있는 것으로 보입니다. 교재와 동일한 결과를 얻기 위해서는 다음과 같은 구조로 직접 코드를 입력하셔야 합니다:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/09/19 22:28:37

// Design Name:

// Module Name: tb_serdes_d81

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_serdes_d81;

// 여기에서 필요한 clk_gen, serdes_tx1, serdes_rx1 모듈 인스턴스를 추가해야 합니다.

clk_gen clk_gen_inst(

// 포트 연결

);

serdes_d81_tx serdes_tx1_inst(

// 포트 연결

);

serdes_d81_rx serdes_rx1_inst(

// 포트 연결

);

endmodule

이처럼 필요한 모듈을 인스턴스화하여 파일에 직접 입력하면 tb_serdes_d81 아래에 clk_gen, serdes_tx1, serdes_rx1 모듈이 포함되게 됩니다.

비교된 이미지들과 교재 페이지들을 토대로 추론해본 코드 예시를 제공해 드렸으니 참고 부탁드립니다. 만약 더 자세한 코드가 필요하시다면 교재의 내용이나 관련된 자료를 참조하시어 포트 연결 부분을 채워주시기 바랍니다.

images:

1. IDE simulation hierarchy

2. EDA tool hierarchy

3. Verilog code snippet

혹시나 추가적으로 궁금한 점이 있으면 언제든지 문의해 주세요. 성공적인 학습 되시길 바랍니다.

강의 추천해주세요

2

27

1

케이테스트 서버 운영 방법

2

49

1

cpu&memory 재설정하기에 질문이 있습니다.

1

52

2

안티그라비티 저는 오픈폴더라고 나와요ㅜ

1

34

2