22장 Vitis C언어 코딩 시 Register map 질문드립니다.

265

작성한 질문수 5

안녕하세요 .

22장에서 BRAM을 하나 더 추가하여서 Core 수를 늘려보자는 취지로 하나 더 늘려보았습니다.

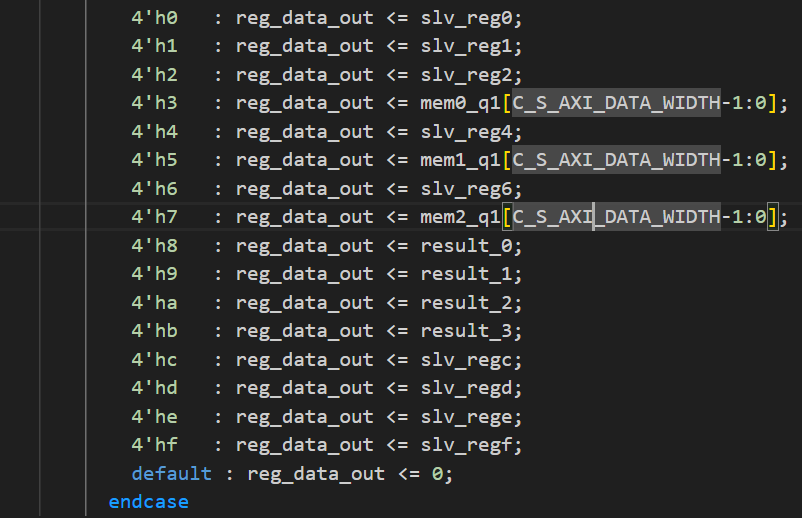

따라서 AXI 코드를

이렇게 설정해주었고 (16bit로 진행했기 때문에 BRAM 하나당 2Core = 4Core 입니다.)

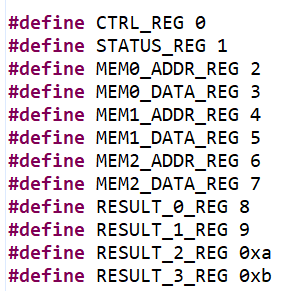

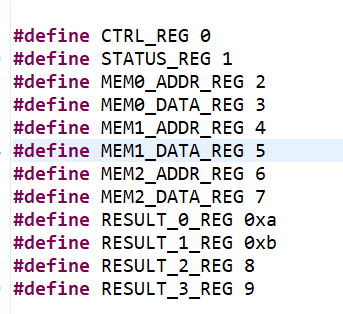

Vitis C언어 상에서도

위와 같이 설정해주었습니다.

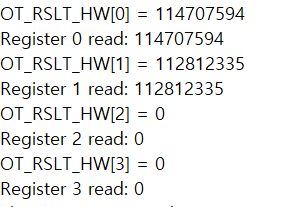

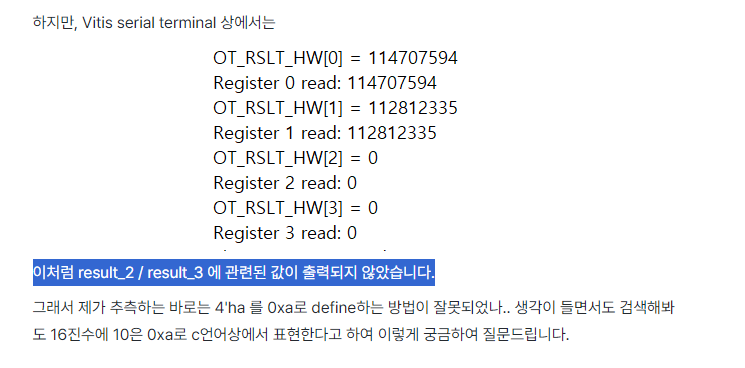

하지만, Vitis serial terminal 상에서는

이처럼 result_2 / result_3 에 관련된 값이 출력되지 않았습니다.

그래서 제가 추측하는 바로는 4'ha 를 0xa로 define하는 방법이 잘못되었나.. 생각이 들면서도 검색해봐도 16진수에 10은 0xa로 c언어상에서 표현한다고 하여 이렇게 궁금하여 질문드립니다.

항상 좋은 강의해주셔서 감사합니다.

답변 1

0

안녕하세요 🙂

개인적으로 수정하신거라 정확한 답변이 어려운점은 양해 부탁드립니다.

질문을 정확하게 이해하지 못했는데요.

8b -> 16b 로 확장까지는 이해했습니다.

여기는 이해를 못했습니다. core 수를 늘리자고 했는데, bit 는 확장했고..

잘 모르는 상태에서 현상만 보았을때는

연결이 잘못된게 아닐까? 라는 생각도 드네요. 실제로 0 이 read 되는 상태라면..?

따라서 기존에 잘 나오는 result1,2 를 2,3 에 연결해보고 값이 동일하게 잘 나오는지 check 해봐도 좋을 것 같습니다. (result 2,3 의 연결 이슈인지 아닌지를 찾기위함)

1

맛비님 답변 정말 감사합니다.

먼저 16Bit로 늘렸던 이유는 8Bit system으로는 정확도가 떨어진다고 생각하여 16Bit로 늘렸고, 그에 따라 32Bit BRAM으로는 Core가 2개로 줄어들기 때문에 BRAM을 하나 더 추가하여 Core 4개를 맞추고자, BRAM을 늘린거였습니다.

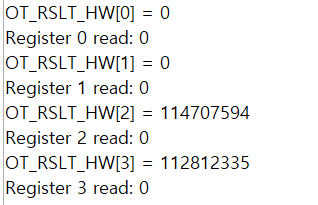

맛비님의 피드백을 보고, 이것저것 실험해보았습니다.

먼저 Vitis Code 상에서 Define을 변경해보았습니다.

또한, 이처럼 그냥 기존에 result2 / result3 값을 계산하는 Core가 계산이 안되는 것인가? 라는 생각을 하게 되었습니다.

Module간에 Result Port도 여러번 확인해보았지만 문제가 없었습니다.

혹시나 Lab22 마지막 쯤에 말씀해주셨던 내용에서 Weight 값을 Update하여 여러번 Core를 돌리면 더 많은 Output Node를 구현할 수 있다고 말씀하셨던것 처럼 Weight를 Update하고 다시 Core를 돌리는 과정에서 BRAM0의 주소를 다시 Clear해야 하는것일까요?

Vitis에 먼저 돌리기 전에, Vivado를 통해 Simulation을 했을 당시에는 Result0/1/2/3 모두 동일한 Clock에 동시에 연산되는것처럼 보였기 때문에 이를 신경쓰지 않았지만 시뮬레이션과 다르게 실제 환경에서는 BRAM1에 Weight값 2개가 먼저 들어가고, 연산 후 BRAM2에 있는 Weight값 2개가 들어가는 형태인지 궁금합니다.

항상 좋은 강의를 해주셔서 감사합니다.

0

result0,1 은 잘나오고, 2,3 은 안나오는 상황이라면,

아키텍쳐를 result0,1 의 Core 모듈과 Memory 를 복제하여 result 2,3 을 구현하는 방법이 맞다면, 서로의 dependency 는 없다고 생각이 드는데요.

연결 이슈가 아닐까요?

UART0, 1 중 선택

1

50

2

datamoverbram모듈질문

1

63

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

84

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

70

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

289

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

145

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

150

2

9장 LED 점등 안됨

1

109

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

89

2

pmu-fw is not running

1

126

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2