한 권으로 끝내는 SVA(System Verilog Assertion) 실무 핸드북

2025. 10. 14. 20:05

수정됨

한 권으로 끝내는 SVA(System Verilog Assertion) 실무 핸드북.zip

93.2MB

12개의 챕터 中 1챕터를 무료 공개합니다.

→ 1챕터 다운받기(Click!)

💻 취업 준비 + 현업에서 필요할 때마다 꺼내 쓰세요.

왜 Assertion인가? RTL 검증의 현실

반도체 회로설계를 공부하신 분들은 많습니다.

SystemVerilog로 테스트벤치 작성, Randomization으로 시나리오 생성, Scoreboard로 결과 비교…

대학이나 대학원에서, 혹은 독학으로 검증 기법들을 열심히 배웁니다.

누구나 한 번쯤은 "완벽한 검증 환경을 만들어보고 싶다" 는 목표를 가집니다.

하지만 실제 프로젝트에 투입되면 현실은 다릅니다.

검증 엔지니어가 마주하는 세 가지 딜레마

딜레마 1: 끝없는 테스트 케이스

테스트벤치를 작성하고, 시나리오를 구성하고, 시뮬레이션을 수천 번 돌립니다.

Coverage 90%, 95%, 98%...

하지만 100%에 도달해도 불안합니다.

"정말 모든 경우를 다 확인한 걸까?"

"놓친 corner case는 없을까?"

밤새 돌린 regression test가 pass해도, 마음 한구석이 편하지 않습니다.

딜레마 2: 디버깅의 늪

어느 날, 시뮬레이션이 실패합니다.

파형을 열어보니 뭔가 잘못되었는데...

10,000 사이클 중 정확히 어디서 문제가 시작되었나?

어떤 신호의 조합이 문제를 일으켰나?

이 버그는 설계 문제인가, 아니면 테스트벤치 문제인가?

파형을 앞뒤로 훑으며 몇 시간을 소비합니다.

"버그를 찾는 시간보다, 버그가 어디서 발생했는지 찾는 시간이 더 길다"는 현실.

딜레마 3: 문서와 코드의 괴리

설계 스펙 문서에는 이렇게 적혀 있습니다:

"요청 후 3~5 사이클 이내 반드시 응답해야 함"

"신호 A와 B는 동시에 HIGH가 되어서는 안 됨"

"리셋 후 첫 번째 사이클에는 모든 출력이 0이어야 함"

이런 규칙들을 테스트벤치로 검증하려면:

// 수백 줄의 체크 로직...

always @(posedge clk) begin

if (req) begin

repeat(5) @(posedge clk);

if (!ack) $error("Response timeout!");

end

end

// 모든 경우에 대해 이런 코드를 일일이 작성해야 합니다

코드가 길어지고, 가독성이 떨어지고, 유지보수가 어려워집니다.

더 큰 문제는: "이 체크 로직이 정말 모든 상황을 커버하나?"

결국 이런 생각에 도달합니다

"테스트 케이스를 아무리 많이 만들어도, 완벽한 검증이라 확신할 수 없다"

"버그를 찾는 것보다, 버그가 없음을 증명하는 게 더 어렵다"

"지금 내가 하는 검증이... 정말 효율적인 방법일까?"

이 세 가지 딜레마에 공감하신다면, 계속 읽어주세요.

이제부터 근본적인 해결책을 소개합니다.

Assertion은 이 세 가지 딜레마를 모두 해결합니다

위에서 제기한 세 가지 딜레마에 대한 답이 바로 SystemVerilog Assertion(SVA)입니다.

Assertion은 검증 방식을 근본적으로 바꿉니다:

전통적 검증 방식 Assertion 기반 검증 "이 입력을 넣으면 → 이 출력이 나온다" 케이스별로 확인 "모든 상황에서 → 이 규칙은 반드시 지켜진다" 선언하고 자동 감시 테스트 케이스를 무한히 늘려도 불안함 규칙 자체를 명시하므로 확신을 가질 수 있음 버그 발생 시점 추적 어려움 위반 즉시 정확한 시점과 조건 보고 수백 줄의 체크 로직 코드 필요 한 줄의 간결한 assertion으로 표현

구체적으로 어떻게 달라지는지 보겠습니다

앞서 제기한 세 가지 딜레마가 어떻게 해결되는지, 실제 사례로 설명하겠습니다.

딜레마 1 해결: "끝없는 테스트 케이스" → 규칙 기반 검증으로 전환

Before (전통적 방식):

// 테스트 케이스 1: A=1, B=0일 때

// 테스트 케이스 2: A=0, B=1일 때

// 테스트 케이스 3: A=1, B=1일 때 (이건 안되는데...)

// ... 무한히 계속

→ 케이스를 아무리 만들어도 "혹시 놓친 게 있을까?" 불안

After (Assertion 방식):

assert property (@(posedge clk) !(A && B));

→ "A와 B가 동시에 1이 되어서는 안 된다"는 규칙 자체를 선언

→ 시뮬레이션 전체 구간, 매 사이클마다 자동으로 검증

→ 테스트 케이스와 무관하게 규칙 위반이 있으면 즉시 탐지

결과: 개별 케이스를 검증하는 게 아니라, 불변 규칙을 감시하므로 확신을 가질 수 있습니다.

딜레마 2 해결: "디버깅의 늪" → 정확한 위반 시점 즉시 파악

Before (전통적 방식):

시뮬레이션 실패 → 파형 열기 → 10,000 사이클 훑어보기

→ "어디서부터 잘못됐지?" → 앞뒤로 확대/축소 반복

→ 몇 시간 후에야 문제 발견

After (Assertion 방식):

Assertion violation at time 4523ns

signal_A = 1, signal_B = 1

Location: protocol_checker.sv:45

Expected: !(signal_A && signal_B)

→ 정확한 시간 (4523ns)

→ 위반 당시의 신호 값

→ 위반된 규칙과 코드 위치

→ 즉시 해당 지점으로 이동해서 원인 분석

결과: 디버깅 시간이 몇 시간에서 몇 분으로 단축됩니다.

딜레마 3 해결: "문서와 코드의 괴리" → 실행 가능한 스펙 문서

Before (전통적 방식):

문서: "요청 후 3~5 사이클 이내 응답해야 함"

코드:

// 이걸 검증하려면...

int counter;

always @(posedge clk) begin

if (req && !req_prev) counter = 0;

if (counter > 0 && counter <= 5) begin

counter++;

if (counter == 6 && !ack)

$error("Timeout!");

end

// ... 복잡한 로직 계속

end

→ 코드가 길고 복잡하고, 문서와 코드가 따로 놈

→ 나중에 스펙이 바뀌면? 문서와 코드 둘 다 수정해야 함

After (Assertion 방식):

// "요청 후 3~5 사이클 이내 응답"

assert property (@(posedge clk)

req |-> ##[3:5] ack

);

→ 스펙을 코드로 직접 표현

→ 문서를 읽는 것처럼 직관적

→ 스펙 변경 시 한 곳만 수정

결과: Assertion은 코드이면서 동시에 살아있는 문서입니다.

플러스 알파! Coverage도 자동 생성

Assertion은 자동으로 Assertion Coverage를 생성합니다.

어떤 assertion이 실제로 검증(pass)되었는지

어떤 assertion은 한 번도 실행(exercise)되지 않았는지

어떤 조건은 테스트되지 않았는지 (vacuous pass)

결과: "우리가 뭘 검증했는지"를 정량적으로 파악할 수 있습니다.

그렇다면 Assertion을 아는 엔지니어의 가치는?

이렇게 강력한 기술이기에, 산업계에서는 SVA를 다룰 수 있는 엔지니어를 적극적으로 찾고 있습니다.

취업 시장의 현실: 왜 기업들은 SVA 경험자를 찾는가

채용 공고를 보면 명확합니다.

삼성전자, SK하이닉스는 물론, NVIDIA, AMD, Intel, Qualcomm 등 글로벌 반도체 기업들이

Verification Engineer 채용 시 "SVA 경험"을 우대 또는 필수 요건으로 명시하고 있습니다.

단순히 "스킬이 좋아 보여서"가 아닙니다. 실질적인 이유가 있습니다.

SVA를 아는 엔지니어는 이런 일을 할 수 있습니다:

복잡한 프로토콜의 타이밍 제약을 정확히 표현하고 검증

"AXI4 프로토콜의 Outstanding Transaction 규칙을 검증해주세요"

SVA를 모르면: 수백 줄의 복잡한 체크 로직 작성, 디버깅에 며칠

SVA를 알면: 핵심 규칙을 assertion으로 명시, 자동 검증, 빠른 디버깅

Formal Verification 등 고급 검증 기법 활용 가능

많은 Formal Tool이 SVA를 입력으로 사용

SVA를 알면 Formal Verification으로 자연스럽게 확장 가능

코드 리뷰에서 설계 의도를 명확히 파악하고 논리적 의견 제시

Assertion을 보면 설계자가 "무엇을 보장하려 했는지" 즉시 이해

"이 assertion이 빠졌네요"라고 근거 있는 리뷰 가능

결과: SVA는 단순한 "추가 스킬"이 아니라, 고급 검증 엔지니어로 인정받는 핵심 역량입니다.

이력서에 "SVA 활용 경험"이 있고 없고의 차이는,

면접에서 "이론만 아는 지원자"와 "실전 검증을 이해하는 지원자"를 구분하는 기준이 됩니다.

이미 현업에 계신 분들에게는?

취업이나 이직뿐만 아니라, 현재 검증 업무를 하고 계신 분들에게도 Assertion은 즉각적인 가치를 제공합니다.

실제 현업에서 이렇게 달라집니다:

상황 1: 회귀 테스트 (Regression Test) 실패 시

Before: "어제까지 pass했는데 오늘 갑자기 fail? 뭐가 바뀌었지?" → 파형 열어서 몇 시간 분석

After: Assertion violation 메시지가 정확한 시점과 원인 알려줌 → 10분 만에 원인 파악

상황 2: 새로운 기능 검증 시

Before: 테스트 케이스 100개 작성 → 시뮬레이션 → "혹시 놓친 케이스 있을까?" 불안

After: 핵심 규칙 5개를 assertion으로 명시 → 테스트 케이스 실행 → 규칙 위반 없음 확인 → 확신

상황 3: 코드 리뷰나 인수 검사

Before: "이 부분이 제대로 검증되었나요?" → "네, 테스트 케이스 20개 pass했습니다" → 여전히 의구심

After: "이 5가지 규칙이 assertion으로 보장됩니다" → 코드로 명시된 근거 → 신뢰도 상승

결과로 얻을 수 있는 것은?

1) 즉각적 효과

⏱️ 반복적으로 파형을 확인하는 시간 대폭 감소

🐛 버그 발생 시점과 원인을 즉시 파악 → 디버깅 시간 단축

✅ 회귀 테스트 시 자동으로 모든 assertion 검증 → 신뢰도 향상

2) 중장기적 효과

📈 커리어 성장: Formal Verification, Low Power Verification 등 고급 검증 분야로 확장 가능

👥 팀 리딩: 검증 방법론 수립, Assertion 코딩 가이드라인 작성 등 리더십 역할

🌏 글로벌 경쟁력: 해외 취업이나 글로벌 프로젝트 참여 시 강력한 차별화 포인트

그런데 왜 모두가 Assertion을 쓰지 않을까?

여기까지 읽으신 분들은 이런 생각이 들 것입니다:

"이렇게 좋으면 당연히 모든 검증 엔지니어가 쓸 텐데?"

하지만 현실은 다릅니다.

많은 팀에서 SVA를 알고는 있지만, 실제로 적극적으로 활용하는 팀은 소수입니다.

이유는 간단합니다: 배우기가 쉽지 않기 때문입니다.

학습의 세 가지 장벽

장벽 1: 낯선 사고방식

일반적인 프로그래밍에 익숙한 사람에게 SVA는 완전히 다른 세계입니다.

// 일반 프로그래밍 사고방식

if (A) then B; // "A이면 B를 실행해라"

// SVA 사고방식

A |-> B; // "A가 참이면, B도 반드시 참이어야 한다"

전자는 "명령(command)", 후자는 "규칙(rule)"입니다.

이 차이를 직관적으로 이해하기까지 시간이 걸립니다.

더군다나 시간적 개념(Temporal Logic)이 들어가면 더 혼란스럽습니다:

##1과##[1:3]의 정확한 차이는?|->와|=>는 한 사이클 차이인데, 언제 어느 걸 써야 하나?Sequence와 Property는 뭐가 다르고, 왜 두 가지가 필요한가?

장벽 2: 단편적인 학습 자료

온라인에서 SVA를 검색하면:

"이런 문법이 있습니다" 수준의 단편적 예제만 있거나

IEEE 1800 LRM 같은 500페이지짜리 표준 문서뿐이거나

영어로 된 해외 강의 자료

"문법은 알겠는데, 실제로 어떻게 쓰는지 모르겠다"는 상황에 자주 부딪힙니다.

실제 학습자들의 고민:

"FSM 검증에 assertion을 쓰고 싶은데, 어디서부터 어떻게 시작해야 하나?"

"Assertion을 작성했는데 예상과 다르게 동작하는데, 디버깅은 어떻게 하나?"

"Immediate와 Concurrent의 차이는 알겠는데, 실제 프로젝트에선 언제 뭘 써야 하나?"

장벽 3: 실무 적용의 막막함

더 큰 문제는 실무 적용입니다.

기존 프로젝트에 assertion을 추가하려면 어떤 식으로 구조화해야 하나?

Bind 문법은 언제 써야 하고, 어떻게 관리해야 하나?

팀원들에게 어떻게 설명하고, 코딩 가이드라인은 어떻게 만드나?

결국 많은 엔지니어들이:

"필요성은 알지만, 어디서부터 어떻게 시작해야 할지 모르겠다"

는 지점에서 멈춰있습니다.

시도해보다가 막히면, "나중에 시간 나면 다시 해봐야지"하고 미루게 됩니다.

이 핸드북이 바로 그 모든 장벽을 해결합니다

!

이 핸드북은 위에서 언급한 세 가지 장벽을 하나씩 허물기 위해 만들어졌습니다.

장벽 1 (낯선 사고방식) → "왜 이렇게 동작하는가"를 근본부터 설명

장벽 2 (단편적 자료) → 체계적인 커리큘럼과 실전 예제

장벽 3 (실무 적용) → FSM, Counter, FIFO 프로젝트로 실무 감각 체득

SVA를 처음 접하는 엔지니어부터 실무에 적용하고 싶은 현업 종사자까지,

모두가 막힘없이, 확실하게 학습할 수 있도록 설계되었습니다.

어떻게 그것이 가능한가요? 4가지 핵심 특징을 소개합니다.

이 핸드북의 4가지 핵심 가치

앞서 제기한 학습의 세 가지 장벽을 하나씩 허물어드립니다.

1. 체계적이고 산업 친화적인 커리큘럼

→ 장벽 1,2 해결: "어디서부터 시작해야 할지 모르겠다"

문제: SVA는 사고방식부터 다르고, 온라인에는 단편적인 자료만 있어서 막막합니다.

해결: 이 핸드북은 단순히 문법을 나열하는 것이 아닙니다.

각 주제마다:

왜 이 기능이 필요한가? (동기 부여)

어떻게 동작하는가? (원리 이해)

실무에서 어떻게 쓰는가? (실전 적용)

순서로 설명합니다.

예를 들어, Implication Operator를 배울 때:

❌ (일반적 자료) "

|->는 overlapping implication입니다. 문법은..."✅ (이 핸드북) "테스트벤치에서 'A가 발생하면 B가 따라온다'를 체크하려면 복잡한 코드가 필요했습니다. SVA의 Implication은 이걸 한 줄로 표현하게 해줍니다. 동작 원리는..."

기초적인 개념(Assertion의 필요성)에서 출발해,

Immediate/Concurrent의 본질적 차이를 명확히 이해하고,

Sequence, Property, Temporal Operator 등 고급 기법으로 확장되며,

마지막에는 실제 프로젝트(FSM, Counter, FIFO)에 적용하는 것까지 다룹니다.

즉, 기초 → 심화 → 실무 적용의 단계별 학습 경로를 통해,

학습자가 자연스럽게 SVA 전문가로 성장할 수 있습니다.

구체적으로 어떤 내용을 어떤 순서로 배우는지 보겠습니다.

SystemVerilog Assertion 학습 목차

Chapter 1. Introduction to the SVA (System Verilog Assertion) Power

→ 무료 다운!

SVA의 필요성과 기본 개념

SVA의 동작 원리와 메커니즘

SVA 문법 구조의 완전한 이해

단계별 예제 분석

실무 적용 가이드

주의사항과 흔한 함정

Chapter 2. Immediate Assertions

Immediate Assertions의 필요성과 기본 개념

Immediate Assertions의 동작 원리

Immediate Assertions의 문법 구조

조합 논리 회로에서의 Immediate Assertions

순차 논리 회로에서의 Immediate Assertions

Assertion 비활성화 메커니즘

Immediate Assertions의 실무 적용

주의사항과 흔한 실수

Chapter 3. Concurrent Assertion

Concurrent Assertion의 필요성과 기본 개념

Concurrent Assertion의 계층 구조 (Layers)

각 계층에서 허용되는 연산자

Concurrent Assertion의 형식과 문법

Property의 단일 및 다중 평가

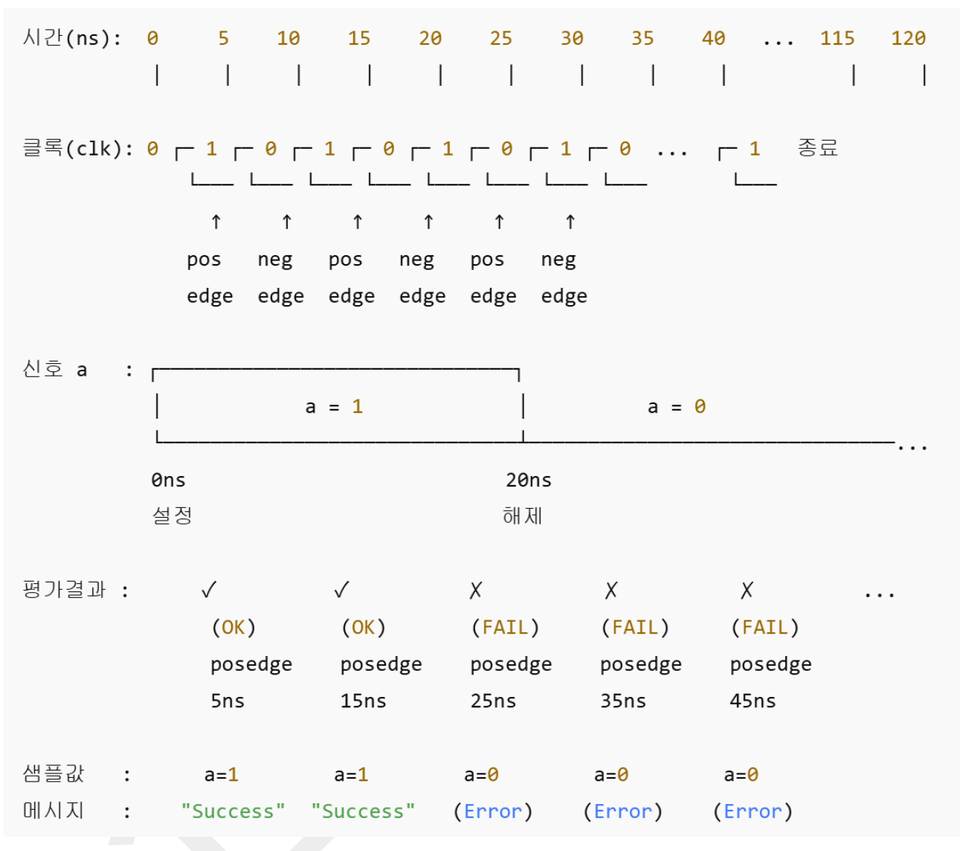

클록 에지의 완전한 이해

Default Clocking의 활용

Concurrent Assertion 비활성화

종합 정리 및 실무 가이드

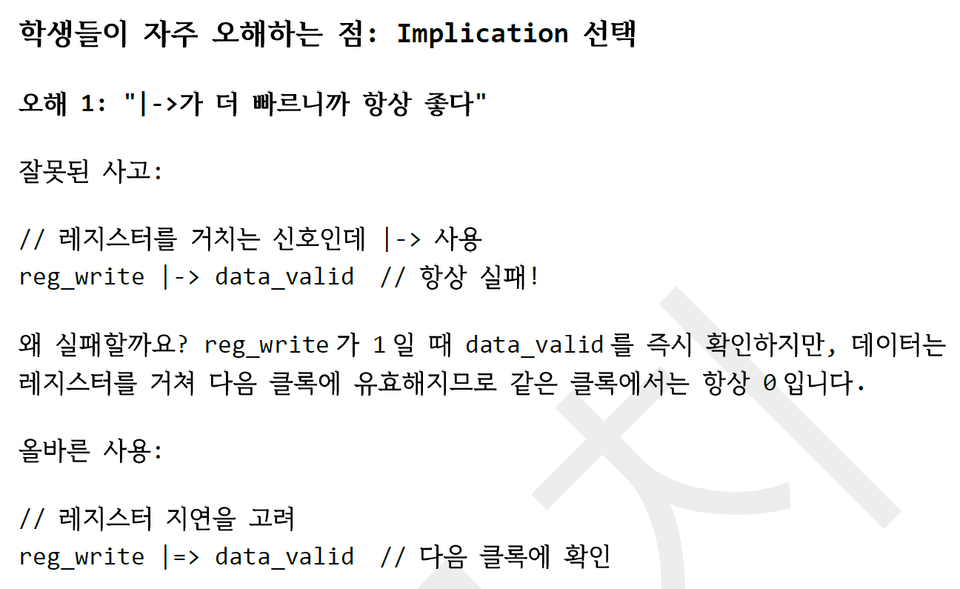

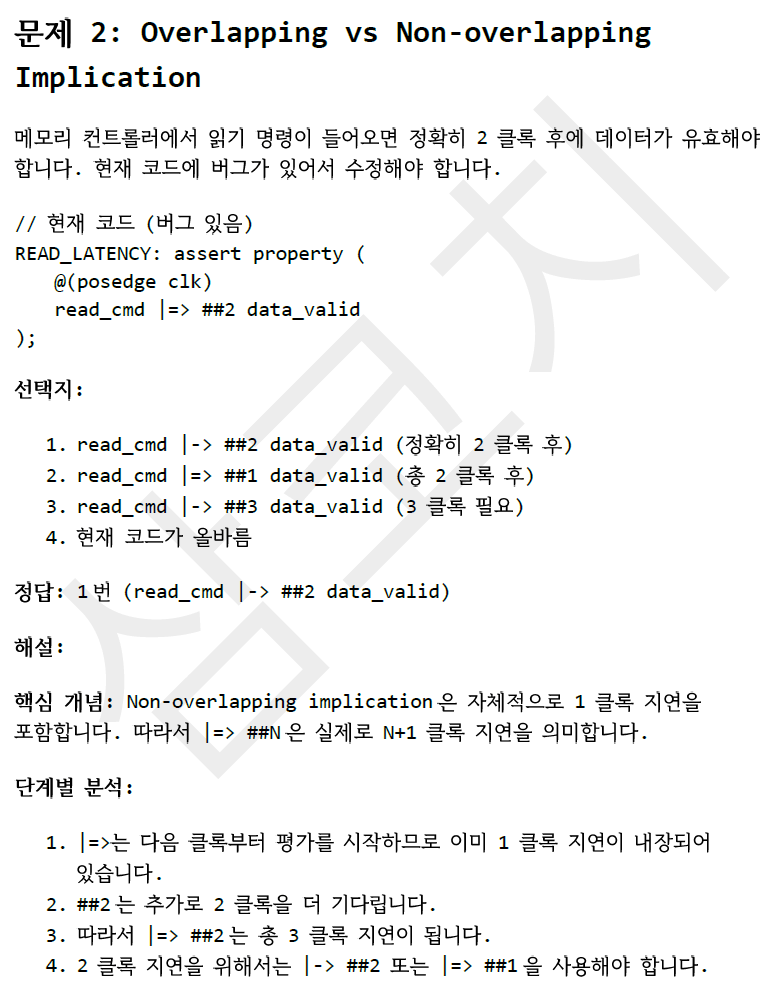

Chapter 4. Implication Operators

Implication Operators의 필요성과 기본 개념

Implication Operators의 동작 원리

Overlapping Implication Operator (|->)

Vacuous Success 문제와 해결

Non-overlapping Implication Operator (|=>)

Property와 Sequence의 매개변수화

Chapter 5. System Task Part 1

System Task의 필요성과 기본 개념

System Task의 동작 원리

$sampled 함수의 완전한 이해

$rose 함수의 완전한 이해

$fell 함수의 완전한 이해

$past 함수의 완전한 이해

클록 지정 메커니즘

실무 적용 사례 심층 분석

주의사항과 함정

종합 정리 및 체크리스트

Chapter 6. System Task Part 2

System Task의 필요성과 기본 개념

신호 변화 감지: $changed와 $stable

원-핫 인코딩 검증: $onehot과 $onehot0

원-콜드 인코딩 검증: $onecold

미정 상태 검출: $isunknown

비트 카운팅: $countbits와 $countones

실무 통합 사례: Assertion과의 결합

주의사항과 함정

종합 정리 및 학습 로드맵

Chapter 7. Sequence Operators

Sequence Operators의 필요성과 기본 개념

Delay Operators의 완전한 이해

Repetition Operators의 체계적 이해

고급 Sequence Operators

종합 실무 예제 분석

주의사항과 실무 가이드

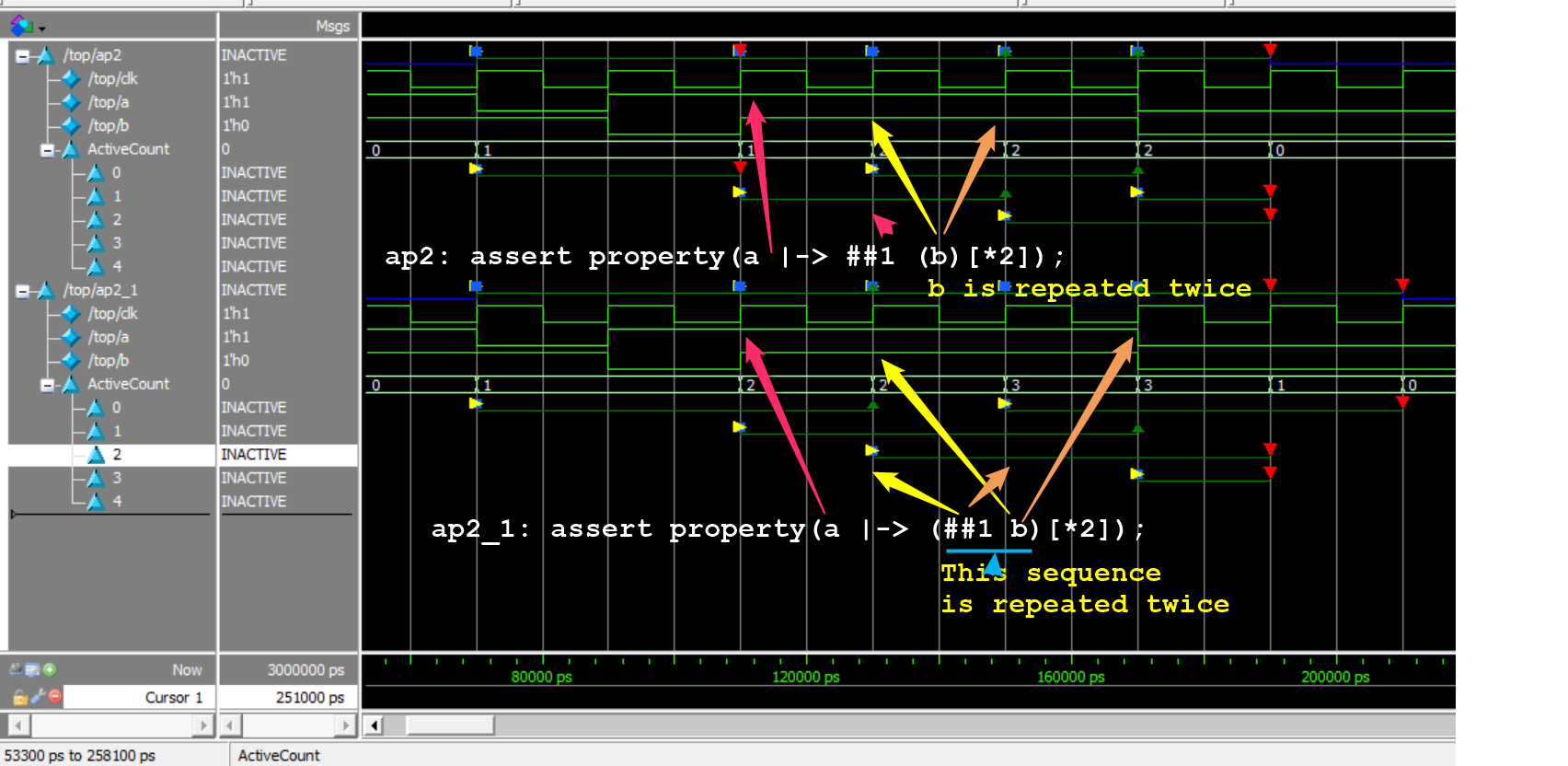

제공 코드 완전 분석 및 고급 활용

고급 디버깅 시나리오와 문제 해결

최종 종합 정리 및 마스터 체크리스트

Chapter 8. Multiple Sequences

복수 시퀀스 조합의 필요성과 기본 개념

불린 연산자를 통한 시퀀스 조합

매칭 연산자를 통한 정교한 타이밍 제어

실무 중심 예제 분석

주의사항과 흔한 함정

종합 정리 및 실전 가이드

추가 실무 예제 및 심화 분석

최종 실무 가이드 및 베스트 프랙티스

Chapter 9. Linear Temporal Logic Operators

Linear Temporal Logic Operators의 필요성과 기본 개념

Eventually Operator의 완전한 이해

Nexttime Operator의 정밀한 타이밍 제어

Until Operator의 조건부 지속 검증

Followed-by Operator의 시퀀스 검증

종합 비교와 실무 가이드

주의사항과 함정

Chapter 10. Local Variables

Local Variables의 필요성과 기본 개념

Local Variables의 동작 원리

문법 구조의 완전한 이해

단계별 예제 분석

실무 적용 가이드

주의사항과 함정

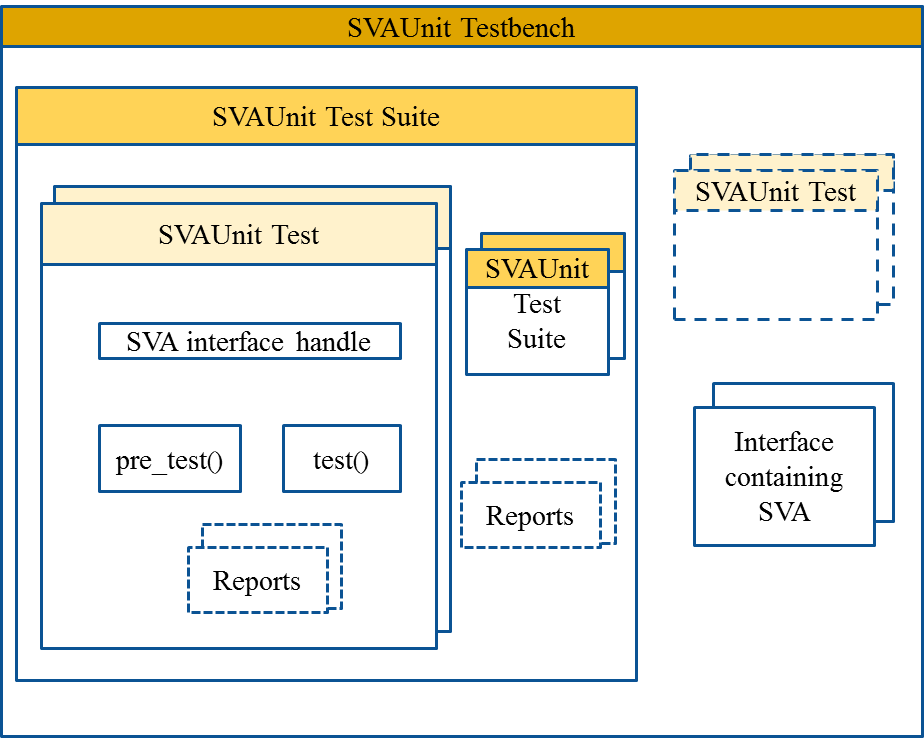

Chapter 11. SVA Projects

Projects의 필요성과 기본 개념

Bind 메커니즘의 완전한 이해

FSM Assertions 프로젝트

Counter Assertions 프로젝트

FIFO Assertions 프로젝트

SystemVerilog 테스트벤치 환경

실무 적용 가이드

2. 실무 환경을 그대로 재현한 코드 예제 → "실제 프로젝트에 어떻게 적용하나" 해결

"문법은 알겠는데, 실제로 어떻게 쓰는지 모르겠다"는 고민을 해결합니다.

이 핸드북은 단순한 이론 설명에 그치지 않습니다.

각 개념마다 실제로 실행 가능한 SystemVerilog 코드를 제공하며,

코드의 동작 원리를 시뮬레이션 결과, 파형, 다이어그램과 함께 단계별로 분석합니다.

예를 들어:

Handshake Protocol:

valid와ready신호의 타이밍 관계를 정확히 검증하는 방법FSM Assertion: 상태 천이의 규칙을 assertion으로 명시하고 검증

FIFO Assertion:

full,empty조건, 데이터 정합성, overflow/underflow 감지Counter Assertion: 증가/감소 조건, 리셋 동작, 범위 초과 체크

System Task 활용:

$rose,$fell,$past등을 실제 프로토콜 검증에 적용

각 예제는:

✅ 완전한 테스트벤치 환경 포함 (설계 모듈 + Assertion 모듈)

✅ 성공 시나리오와 실패 시나리오 모두 제공

✅ 왜 이렇게 작성했는지, 설계 의도와 논리적 근거 상세 설명

✅ 실무에서 바로 수정하여 사용 가능한 템플릿 형태

즉, 단순히 "이런 문법이 있다"를 배우는 것을 넘어서,

"실제 프로젝트에서 이렇게 쓴다"를 체득할 수 있습니다.

3. 학습 효과를 극대화하는 퀴즈와 실습 과제 → "왜 그렇게 동작하는지" 깊이 이해

단순히 문법을 외우는 것이 아니라, 원리를 이해하고 스스로 적용할 수 있게 만듭니다.

핸드북에는 단순 암기 확인 문제가 아니라,

개념의 이해도를 정확히 점검하고 실무 감각을 키우는 문제들이 포함되어 있습니다.

각 챕터마다 제공되는 것:

핵심 개념 확인 퀴즈 (선다형, 서술형)

"왜 이렇게 동작하는가?"를 묻는 심화 문제

실제 설계 시나리오에서 assertion을 작성하는 실습 과제

이를 통해 독자는:

단순히 문법을 외우는 것이 아니라, 왜 그렇게 동작하는지 원리를 이해합니다

새로운 설계를 마주했을 때, 스스로 assertion을 설계할 수 있는 능력을 기릅니다

팀에서 코드 리뷰나 설계 논의 시, 논리적으로 근거를 제시할 수 있게 됩니다

즉, 이 핸드북은 지식 전달을 넘어,

학습자가 실무에서 독립적으로 문제를 해결할 수 있는 능력을 키우는 훈련 도구입니다.

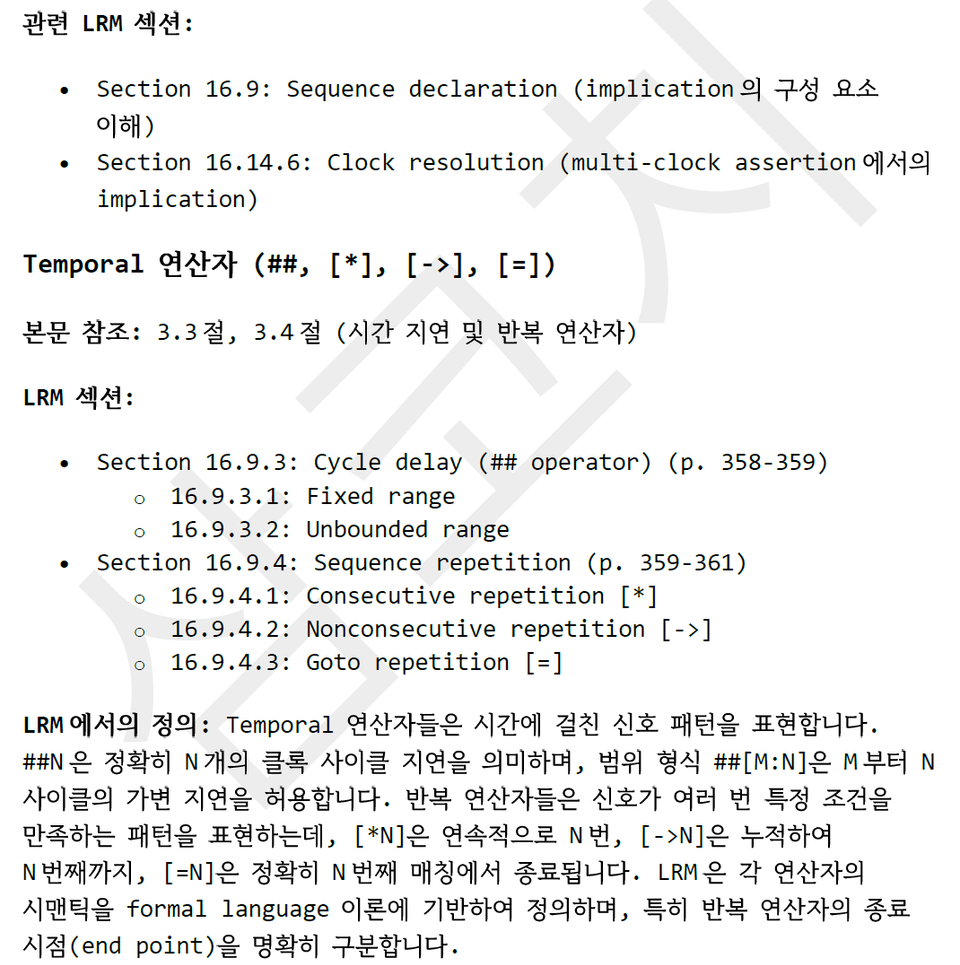

4. IEEE 표준 기반의 정확성과 신뢰성 → "표준 문서의 벽" 극복

IEEE 1800 LRM은 방대하고 어렵지만, 반드시 필요한 레퍼런스입니다.

이 핸드북은 LRM의 내용을 이해하기 쉽게 풀어서 설명하면서도, 표준 근거를 명확히 제시합니다.

이 핸드북은 단순히 경험이나 관습적 설명에 의존하지 않습니다.

모든 주요 내용은 IEEE 1800-2017 SystemVerilog Language Reference Manual (LRM)과 연결되어 있으며,

각 기능에 대응하는 LRM 섹션을 명확히 제시합니다.

덕분에:

✅ 단순히 "어떻게 쓰는지"를 넘어, 왜 그렇게 정의되었는지 이해할 수 있습니다

✅ Tool마다 동작이 다를 때, 표준을 기준으로 올바른 해석을 할 수 있습니다

✅ 팀 내 코드 리뷰나 설계 논의 시, 표준 문서를 근거로 명확한 의견을 제시할 수 있습니다

이는 현업에서 자주 마주하는 상황:

Assertion Coding Guideline 작성

팀 내 기술 표준 수립

Tool 간 이식성(Portability) 이슈 해결

Formal Verification Tool과의 연계

에서도 강력한 무기가 됩니다.

즉, 이 핸드북은 단순한 학습 자료를 넘어,

실무자가 신뢰할 수 있는 표준 기반의 레퍼런스 가이드로 기능합니다.

이런 분들께 추천합니다

취업 준비생:

🎯 Verification Engineer로 취업/이직을 준비하는 분

🎯 이력서와 면접에서 차별화 포인트를 만들고 싶은 분

🎯 글로벌 반도체 기업(삼성, SK하이닉스, NVIDIA, AMD 등)을 목표로 하는 분

현업 종사자:

🎯 검증 업무를 하지만 assertion은 아직 체계적으로 배우지 못한 분

🎯 업무 효율을 높이고, 디버깅 시간을 줄이고 싶은 분

🎯 Formal Verification, Low Power Verification 등 고급 검증 분야로 확장하고 싶은 분

🎯 팀에 assertion 문화를 도입하고 싶은 리드 엔지니어

설계 엔지니어:

🎯 설계한 모듈의 동작을 assertion으로 명확히 문서화하고 싶은 분

🎯 검증팀과 효과적으로 협업하고 싶은 분

궁금하신 점이 있으신가요?

구매 전 자주 묻는 질문들을 정리했습니다.

Q: SystemVerilog 기초만 알아도 따라갈 수 있나요?

A: 네, 기본적인 SystemVerilog 문법(always block, procedural assignment, data type 등)을 알고 있다면 충분합니다. Assertion 관련 내용은 기초부터 단계별로 설명합니다.

Q: Verification 경험이 없어도 괜찮나요?

A: 1챕터에서 검증의 기본 개념과 assertion의 필요성을 설명하므로, 검증 경험이 없어도 학습 가능합니다. 다만, 기본적인 디지털 회로 설계 지식은 필요합니다.

Q: 어떤 시뮬레이터를 사용하나요?

A: 예제는 주요 상용 시뮬레이터(ModelSim, Synopsys VCS, Cadence Xcelium 등)에서 동작하도록 작성되었습니다.

Q: 실무 프로젝트에 바로 적용할 수 있나요?

A: 네, 11챕터의 FSM, Counter, FIFO 프로젝트는 실제 설계에서 자주 마주하는 패턴을 다룹니다. 제공된 코드를 템플릿으로 사용하여 자신의 프로젝트에 적용할 수 있습니다.

Q: Formal Verification도 다루나요?

A: SVA 자체에 집중하며, Formal Verification은 간략히 소개하는 수준입니다. 하지만 SVA를 마스터하면 Formal Verification의 기초가 탄탄해지므로, 다음 단계로 진행하기 수월합니다.