한 권으로 끝내는 UVM Verification 실무 핸드북

2025. 10. 12. 22:04

수정됨

한 권으로 끝내는 UVM 실무 핸드북.zip

71.7MB

9개의 챕터 中 1개 챕터를 무료 공개합니다.

→ 1개 챕터 다운받기(Click!)

💻 취업 준비 + 현업에서 필요할 때마다 꺼내 쓰세요.

왜 UVM인가? SystemVerilog Testbench의 한계

반도체 설계를 공부하면서 SystemVerilog로 RTL을 작성하고,

Testbench를 만들어 시뮬레이션을 돌려본 경험이 있을 것입니다.

간단한 모듈이라면 충분합니다.

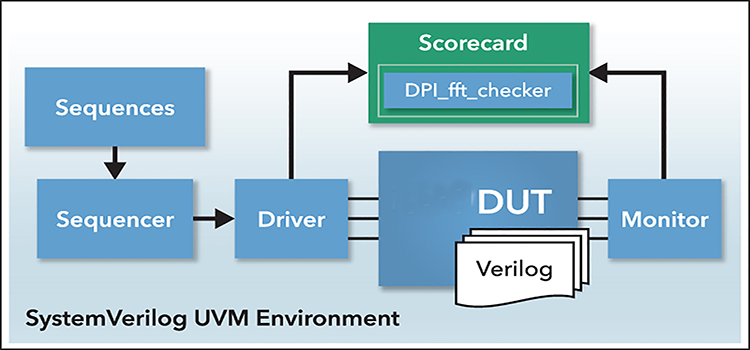

Driver로 입력을 넣고, Monitor로 출력을 확인하고, Scoreboard로 결과를 검증하는 구조로

학교 프로젝트나 개인 과제를 성공적으로 완료할 수 있습니다.

![Verification] Hướng dẫn tạo testbench tự kiểm tra thiết kế bằng Verilog, System Verilog ~ VLSI TECHNOLOGY](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEg6ACDAjsZn-NLSxQAfLjp9yLlZFtGCpZfyH0pRZdRyIlOY-cgibWgWBAnkYe7jBVKLH_hMFm9bszPwsvEgkC0cYmjmnnL8ykeMuF31M7B87UxMXMnfQKC_zDTvPOVBFWI284nBuAY4FUHk/s1600/image.png)

그런데 현업에 들어가거나, 복잡한 IP를 다루게 되면 전혀 다른 문제와 마주하게 됩니다.

"이 코드를 다른 프로젝트에서 재사용할 수 있나?"

"새로운 팀원이 내 검증 환경을 이해하고 확장할 수 있나?"

"여러 IP를 통합 검증할 때 각 컴포넌트를 어떻게 관리하지?"

실무 프로젝트가 커질수록, 체계 없이 작성된 Testbench는 유지보수가 불가능해집니다.

프로젝트마다 검증 환경을 처음부터 다시 작성하는 것은 시간과 비용의 낭비입니다.

팀마다 다른 방식으로 작성된 코드는 협업을 어렵게 만듭니다.

이런 문제들은 개인의 역량 부족이 아닙니다.

구조화되지 않은 검증 방법론 자체의 한계입니다.

UVM이 해결하는 실무 문제들

바로 이 지점에서 UVM이 등장합니다.

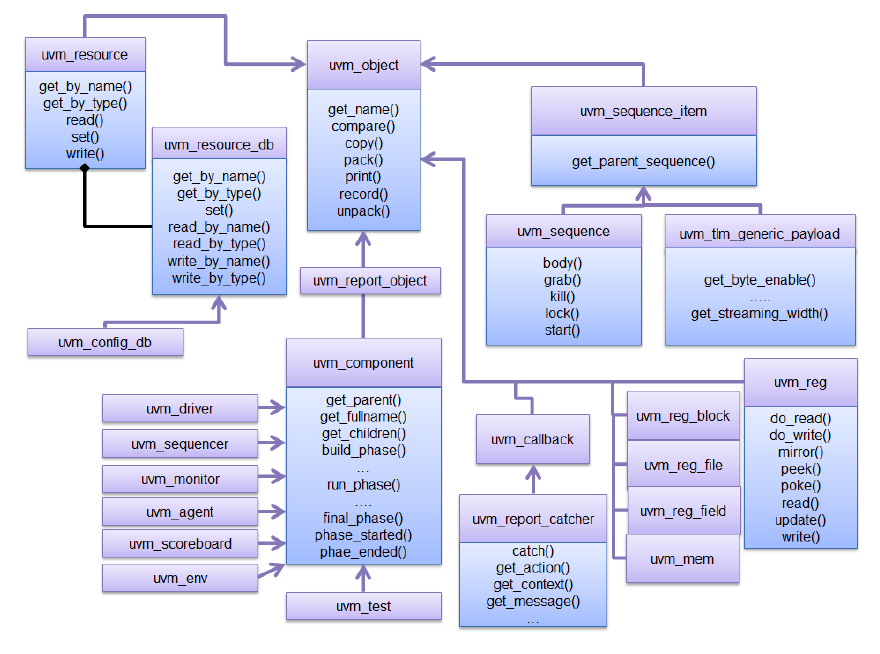

UVM(Universal Verification Methodology)은 Accellera에서 표준화한 검증 방법론입니다.

Mentor Graphics, Cadence, Synopsys 등 EDA 업체들이 공동으로 개발했으며,

현재 전 세계 반도체 기업에서 SoC 검증의 사실상 표준으로 사용되고 있습니다.

단순히 "유명하거나 많이 쓰이는" 수준이 아닙니다.

실무에서 반드시 겪게 되는 검증의 근본적인 문제들을 해결하기 위해 설계된 방법론입니다.

System Verilog vs. UVM, 차이점은?

1. 표준화된 검증 아키텍처

모든 UVM 환경은 동일한 구조를 따릅니다. Driver, Monitor, Sequencer, Agent, Environment 등의 컴포넌트가 명확한 역할 분담을 가지고, 정해진 방식으로 통신합니다. 이는 코드 리뷰와 팀 협업을 획기적으로 개선합니다.

2. 재사용 가능한 IP 검증 컴포넌트 (VIP)

한 번 작성한 UVM Agent는 다른 프로젝트에서 그대로 재사용할 수 있습니다. AXI, PCIe, USB 같은 표준 프로토콜의 경우, 상용 VIP를 구매하거나 내부적으로 구축한 VIP 라이브러리를 활용할 수 있습니다.

3. Phase 기반 시뮬레이션 제어

UVM Phase 시스템은 검증 환경의 생성(build), 연결(connect), 실행(run), 결과 분석(report)을 체계적으로 관리합니다. 복잡한 환경에서도 초기화 순서와 종료 조건을 명확하게 제어할 수 있습니다.

4. TLM(Transaction Level Modeling)

Signal-level이 아닌 Transaction-level에서 컴포넌트 간 통신을 추상화합니다. 이는 시뮬레이션 속도를 향상시키고, 검증 환경의 복잡도를 낮춥니다.

5. Sequence 기반 테스트 시나리오 관리

복잡한 테스트 시나리오를 계층적으로 구성하고, 런타임에 동적으로 변경할 수 있습니다. Randomization과 Constraint를 활용한 자동 테스트 생성도 가능합니다.

6. Configuration Database와 Factory Pattern

런타임에 검증 환경을 재구성하거나 컴포넌트를 교체할 수 있습니다. 동일한 테스트 코드로 다양한 설정을 검증할 수 있어, 회귀 테스트(Regression Test) 환경 구축이 용이합니다.

이처럼 UVM은 단순히 "코딩 스타일"이 아니라,

검증의 생산성과 품질을 근본적으로 향상시키는 체계적인 방법론입니다.

그렇다면 당연한 질문이 생깁니다.

"이렇게 중요한 기술을 배우면, 시장에서 어떤 가치를 인정받을까?"

UVM 검증 엔지니어의 시장 가치

UVM을 능숙하게 다루는 검증 엔지니어는 반도체 산업에서 항상 부족합니다.

왜일까요?

단순히 테스트를 작성하는 것이 아니라, 재사용 가능한 검증 인프라를 설계하고,

팀의 검증 생산성을 향상시키는 핵심 역할을 수행하기 때문입니다.

이는 프로젝트의 일정과 비용, 나아가 칩의 품질을 직접적으로 좌우합니다.

시장은 이런 희소성과 중요성을 정확히 반영합니다.

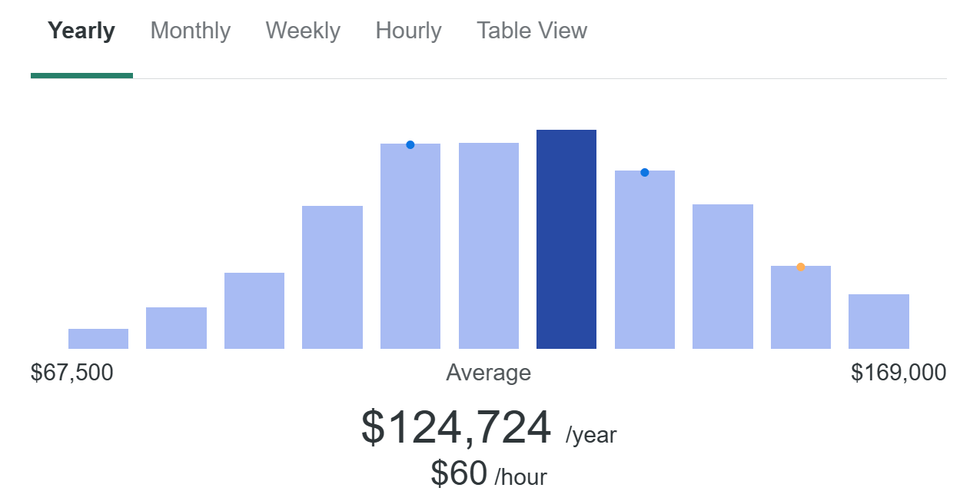

연봉 데이터

미국 시장 (Glassdoor, Indeed 기준, 2024)

Entry-level UVM Verification Engineer: $120,000 - $145,000

Mid-level (3-5년 경력): $145,000 - $180,000

Senior-level (7+ 년 경력): $180,000 - $250,000+

국내 시장 (대기업 기준)

신입~3년차: 5,000만 원 ~ 7,000만 원

4~7년차: 7,000만 원 ~ 1억 원

8년차 이상: 1억 원 ~ 1.5억 원

취업 시장 현황

글로벌 반도체 기업 (삼성전자, SK하이닉스, TSMC, Intel, NVIDIA, Qualcomm 등)의

검증 엔지니어 채용 공고를 보면

필수 요구사항: SystemVerilog, UVM, Functional Coverage

우대사항: UVM VIP 개발 경험, 특정 프로토콜(AXI, PCIe, DDR 등) 검증 경험

UVM 역량은 단순한 우대사항이 아니라, 사실상 필수 요구사항입니다.

이력서에 "UVM 기반 검증 환경 구축 경험"이 있으면 서류 통과율이 크게 높아집니다.

현업에서의 가치

취업 준비생 관점

포트폴리오에 UVM 프로젝트 추가 → 면접 기회 증가

실무 프로젝트를 처음부터 구축한 경험 → 즉시 투입 가능한 인재로 평가

표준화된 방법론 숙지 → 빠른 온보딩과 팀 적응

현업 엔지니어 관점

검증 코드 재사용 → 프로젝트 일정 단축

표준화된 구조 → 팀원 간 협업 효율 향상

VIP 라이브러리 구축 → 조직의 검증 역량 축적

복잡한 SoC 검증 → 고난도 프로젝트 수행 능력 입증

여기까지 읽으면 이런 생각이 들 수 있습니다.

"좋은 건 알겠는데, 그럼 바로 배워서 쓰면 되는 거 아닌가?"

맞습니다. 이론적으로는 그렇습니다.

하지만 많은 사람들이 UVM 학습 도중에 포기하거나, 표면적인 이해에 그치는 이유가 있습니다.

하지만 막상 배워보면 어렵습니다.

UVM의 가치를 인정하고 배우기 시작했다가도,

많은 학습자들이 중간에 좌절을 경험합니다.

SystemVerilog 문법을 안다고 해서 UVM을 바로 사용할 수 있는 것은 아닙니다.

마치 C 언어를 안다고 해서 리눅스 커널 개발을 바로 할 수 없는 것과 같습니다.

어려움 1 : UVM의 진입 장벽

1. 개념적 복잡성

UVM은 객체지향 프로그래밍(OOP), 디자인 패턴, Transaction Level Modeling 등 여러 고급 개념이 결합되어 있습니다. 각각을 이해하는 것도 어렵지만, 이들이 어떻게 유기적으로 연결되는지 파악하기는 더욱 어렵습니다.

2. Phase 시스템의 복잡한 실행 흐름

build_phase, connect_phase, run_phase, extract_phase 등 10개 이상의 Phase가 정해진 순서로 실행됩니다. 각 Phase에서 무엇을 해야 하는지, 왜 이런 순서인지를 이해해야 올바른 검증 환경을 구축할 수 있습니다.

3. TLM Port/Export 연결의 추상화

Signal-level 연결에 익숙한 엔지니어에게 TLM의 추상적 연결 방식은 혼란스럽습니다. Port, Export, Analysis Port의 차이와 사용법을 이해하지 못하면 컴파일 에러와 런타임 에러에 시달리게 됩니다.

4. Sequence와 Sequencer의 동작 메커니즘

Sequence를 어떻게 작성하고, Sequencer와 Driver가 어떻게 협업하는지, Handshake가 어떻게 이루어지는지 이해하는 데 시간이 걸립니다.

5. Configuration Database와 Factory Pattern

config_db를 통한 설정 전파, Factory를 통한 객체 생성과 타입 교체 등은 SystemVerilog에 없던 개념이라 낯설고 어렵습니다.

어려움2 : 파편화된 학습 자료의 문제

인터넷에는 UVM 관련 자료가 많지만, 대부분 특정 기능만 설명하거나, 완전하지 않은 예제를 제공합니다.

공식 UVM User Guide는 600페이지가 넘고, IEEE 1800.2 표준 문서는 더욱 방대합니다.

(https://www.accellera.org/images/downloads/standards/uvm/uvm_users_guide_1.2.pdf)

어디서부터 시작해야 할지, 무엇이 중요한지 판단하기 어렵습니다.

더 큰 문제는 "왜 이렇게 설계되었는지"를 설명하는 자료가 거의 없다는 것입니다.

"이렇게 하세요"만 있고 "왜 이렇게 해야 하는지"가 없으면,

비슷한 상황에서 스스로 판단할 수 없습니다.

결국 많은 학습자들이:

예제 코드를 복사-붙여넣기만 하다가 응용하지 못하거나

에러가 나면 원인을 찾지 못해 포기하거나

표면적으로만 이해하고 실무에서 제대로 활용하지 못합니다

"그렇다면 체계적으로, 근본부터 이해하면서 배울 수 있는 방법은 없을까?"

바로 이 질문에 대한 답이 이 핸드북입니다.

이 핸드북이 특별한 이유

이 핸드북은 단순한 UVM 튜토리얼이 아닙니다.

UVM을 완전히 이해하고, 실무에 바로 적용할 수 있도록 설계된 완전한 학습 시스템입니다.

1. 체계적이고 논리적인 학습 구조

이 핸드북은 UVM의 각 요소를 왜 필요한지부터 시작하여, 어떻게 동작하는지, 어떻게 사용하는지를 단계적으로 설명합니다.

학습 흐름:

기초 도구 습득 → Reporting Mechanism으로 디버깅 방법 먼저 학습

핵심 구성 요소 이해 → UVM_OBJECT와 UVM_COMPONENT의 본질적 차이 파악

환경 구축 메커니즘 → config_db로 설정을 전파하는 방법 이해

실행 흐름 제어 → Phase 시스템의 설계 철학과 동작 원리 학습

컴포넌트 간 통신 → TLM을 통한 추상화된 통신 구현

테스트 시나리오 작성 → Sequence 기반의 유연한 시나리오 관리

실전 프로젝트 → Combinational Adder와 Sequential Adder의 완전한 검증 환경 구축

이 순서는 무작위가 아닙니다. 각 단계가 다음 단계의 기초가 되도록 설계되어,

학습자가 개념의 누적 없이 자연스럽게 UVM 전체를 이해할 수 있습니다.

하지만 체계적인 학습 구조만으로는 충분하지 않습니다.

실제로 동작하는 코드를 직접 만들어보지 않으면, 진짜 이해했다고 할 수 없습니다.

UVM 학습 목차

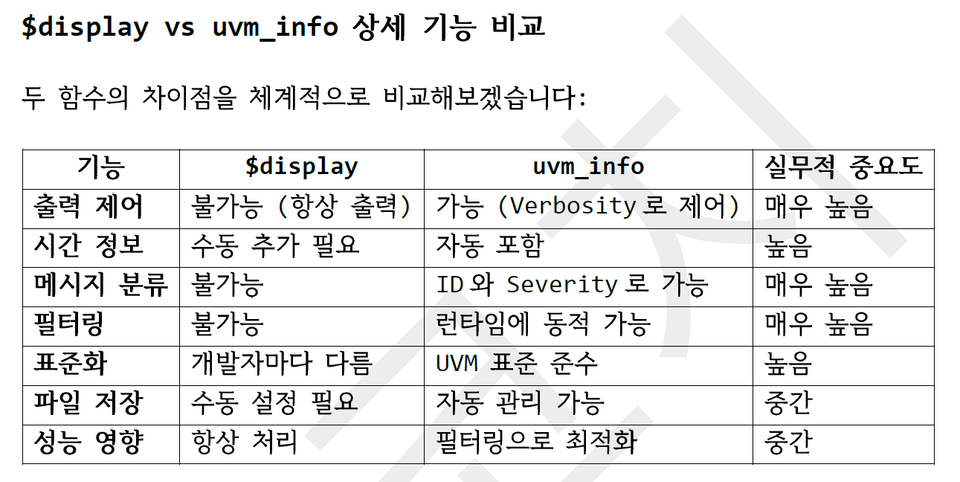

Chapter 1: Reporting Mechanism

UVM Reporting System 근본 이해

기본 Reporting Macros와 Display 함수 완전 비교

동적 메시지 생성과 포맷팅 시스템

Verbosity Level 체계의 완전한 이해

ID 기반 선택적 메시지 제어 메커니즘

Component별 독립적 Reporting 관리

Hierarchy 기반 일괄 제어 시스템

Severity Level을 통한 체계적 상황 분류

Severity Override를 통한 런타임 동작 변경

Quit Count를 통한 시뮬레이션 흐름 제어

File 기반 Logging으로 영구 기록 관리

Chapter 2: UVM_OBJECT

UVM_OBJECT 기초 - 왜 필요하고 무엇인가?

Randomization 시스템 완전 이해

Factory Pattern과 Object Creation

Field Macro System - 자동화의 핵심

Object 출력과 디버깅 전략

Object 복사 메커니즘의 모든 것

Object 비교와 검증 전략

UVM_OBJECT 실무 활용 가이드

Chapter 3: UVM_COMPONENT

왜 UVM Component가 필요한가 - 근본적 이해

첫 번째 코드로 보는 UVM Component 기초

UVM Tree 구조의 핵심 원리

두 번째 코드로 보는 계층 구조 실습

Phase 시스템 동작 원리

하드웨어와 소프트웨어 관점 비교

실무에서 자주 하는 실수들

고급 활용 패턴 및 실제 프로젝트 사례

성능 최적화 및 대규모 프로젝트 관리

Chapter 4: UVM config_db

SystemVerilog에서 UVM으로의 패러다임 변화 이해

config_db의 본질과 존재 이유

기본 데이터 전달 메커니즘 완전 분석

Virtual Interface 전달의 핵심 원리

계층구조와 Naming Convention의 실제

실무에서의 디버깅과 문제해결 전략

Chapter 5: UVM PHASES

검증의 기본 원리와 Phase 시스템의 필연성

Phase 분류 체계의 설계 철학과 실행 원리

Construction Phases - 검증 환경 구축의 세부 메커니즘

Runtime Phases - 시간 기반 검증 실행의 핵심

Objection 메커니즘 - 분산 시간 제어의 정교한 설계

Time Management - 시뮬레이션 시간 제어의 고급 기법

Cleanup Phases - 검증 결과 처리의 체계적 접근

학생들이 빠지기 쉬운 함정들과 해결책

Chapter 6: UVM TLM (Transaction Level Modeling)

TLM의 기본 개념과 필요성

Port와 Export의 기본 구조

Blocking PUT Operation - 단방향 데이터 전송

Implementation (IMP) 추가 - 실제 동작 구현

Direct Port-to-IMP Connection

Hierarchical Connection - 계층적 연결

Export-IMP Pattern - 중간 매개체 활용

GET Operation - 데이터 요청과 응답

Transport Operation - 양방향 통신

Analysis Port - 브로드캐스팅

실무 활용 전략과 최종 정리

Chapter 7: UVM Sequence

UVM Sequence의 필요성과 기본 개념

Transaction: 하드웨어 통신의 기본 단위

Sequence 클래스의 내부 구조

Driver와 Sequencer: 데이터 전달 체계

Sequence 실행 방법들의 비교

병렬 처리와 우선순위 시스템

Sequencer Arbitration의 이해

고급 제어 메커니즘들

Chapter 8: Project - Combinational Adder → 무료 공개

하드웨어 검증의 기본 개념과 UVM의 필요성

DUT와 Interface 분석 - 검증 대상의 완전한 이해

UVM Transaction Class - 데이터 모델링의 출발점

UVM Sequence Class - 테스트 시나리오 생성기

UVM Driver Class - 소프트웨어와 하드웨어 간의 브릿지

UVM Monitor Class - 하드웨어 신호 관찰자

UVM Scoreboard Class - 결과 검증과 판정

UVM Agent Class - 검증 컴포넌트 관리자

UVM Environment Class - 검증 환경 통합 관리

UVM Test Class - 검증 시나리오 제어기

Testbench Top Module - 하드웨어와 소프트웨어의 만남

전체 시뮬레이션 플로우와 실무 적용

Chapter 9: Project - Sequential Adder

왜 UVM인가? Sequential Adder 검증의 필요성

Sequential Adder DUT 완전 분석

Interface: 하드웨어와 테스트벤치의 연결고리

Transaction: 데이터 패킷의 정의

Generator: 테스트 시나리오 생성기

Driver: 실제 신호를 DUT에 전달

Monitor: DUT 출력 감시자

Scoreboard: 결과 검증 판정관

Agent: Driver와 Monitor의 관리자

Environment: 전체 테스트 환경 구성

Test: 최상위 테스트 시나리오

Testbench Top: 모든 것을 연결하는 최종 모듈

실행 분석 및 디버깅 전략

실무 적용 및 확장 방안

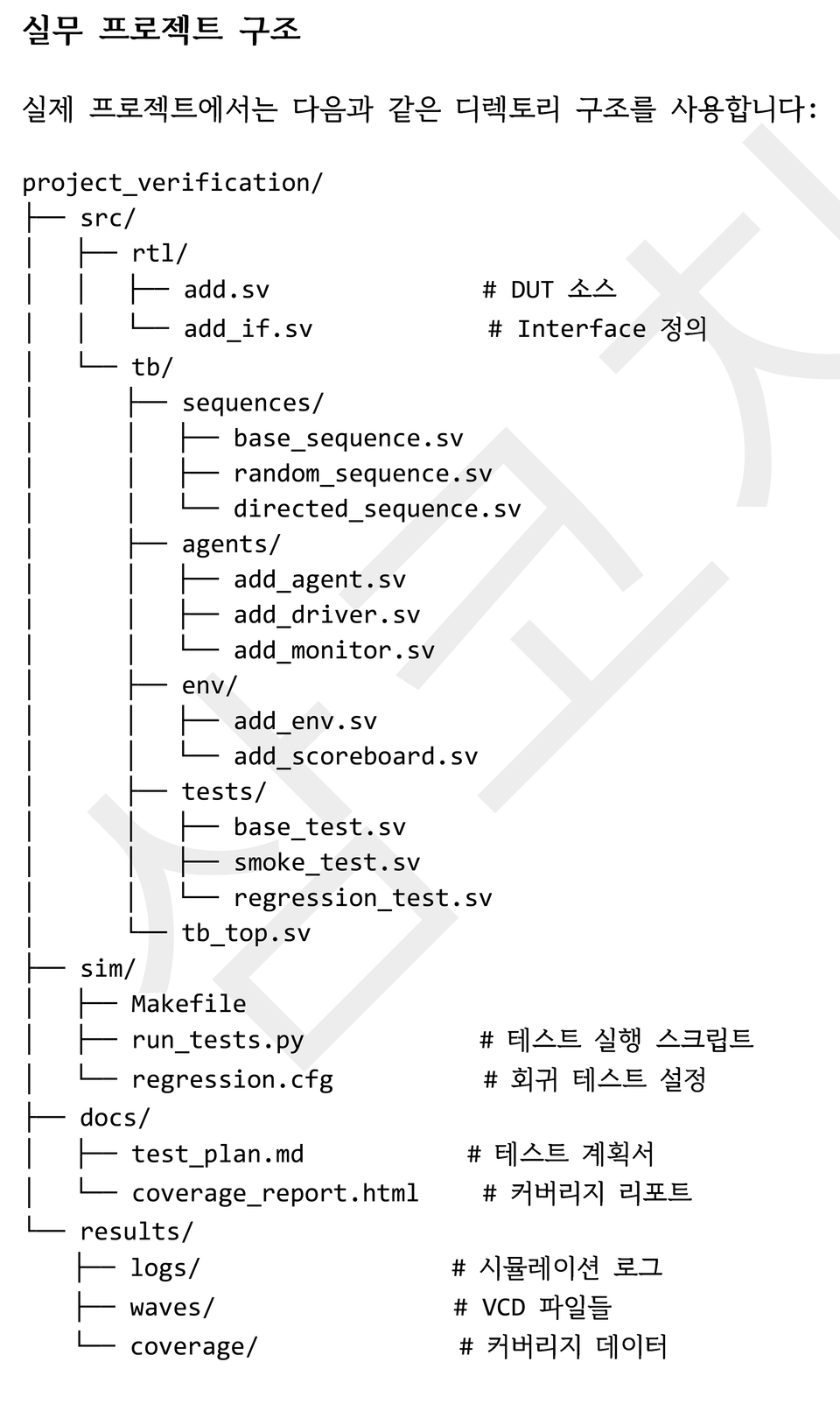

2. 실무 중심의 완전한 프로젝트 예제

이론만 아는 것과 실제로 구현할 수 있는 것은 전혀 다릅니다.

이 핸드북은 실제 동작하는 완전한 UVM 검증 환경을 단계별로 구축하는 과정을 제공합니다.

Project 1: Combinational Adder 검증

하드웨어 검증의 기본 개념부터 시작

DUT와 Interface 분석

Transaction, Sequence, Driver, Monitor, Scoreboard, Agent, Environment, Test의 단계적 구현

Testbench Top Module에서의 통합

전체 시뮬레이션 플로우 분석

Project 2: Sequential Adder 검증

상태 기계(FSM)를 가진 설계의 검증

Clock과 Reset 처리

복잡한 Protocol Handling

Corner Case 검증 시나리오

실무 수준의 Scoreboard 구현

각 프로젝트는:

완전한 소스 코드 제공 (복사-붙여넣기로 즉시 실행 가능)

코드의 각 라인 설명 (왜 이렇게 작성했는지)

시뮬레이션 결과 분석 (로그 해석 방법)

실무 확장 방안 (실제 프로젝트에 적용하는 방법)

프로젝트를 완성하면 포트폴리오에 바로 사용할 수 있습니다.

하지만 코드를 작성할 수 있다고 해서 끝이 아닙니다.

"왜 이렇게 설계되었는지"를 이해해야 진짜 실력입니다.

3. 근본적 이해를 위한 "왜"의 강조

많은 자료가 "이렇게 하세요"만 알려주고 "왜 이렇게 해야 하는지"는 설명하지 않습니다.

이 핸드북은 모든 주제에서 설계 철학과 동작 원리를 먼저 설명합니다.

예시:

일반적인 설명:

"config_db::set()을 build_phase에서 호출하세요."

이 핸드북의 설명:

"config_db는 UVM 계층 구조에서 설정을 전파하는 메커니즘입니다. build_phase는 상위 컴포넌트부터 하위 컴포넌트 순서로 실행되므로, 부모가 설정을 config_db에 저장하면 자식이 build_phase에서 이를 가져올 수 있습니다. connect_phase에서는 이미 모든 컴포넌트가 생성된 후이므로 config_db를 통한 객체 전달이 의미가 없습니다. 따라서 config_db::set()은 반드시 build_phase에서 호출해야 합니다."

이렇게 원리를 이해하면, 비슷한 상황에서 스스로 올바른 판단을 할 수 있습니다.

단순 암기가 아닌 본질적 이해를 목표로 합니다.

원리를 이해했다면, 이제 실수를 피할 차례입니다.

학습 과정에서 누구나 겪는 전형적인 함정들을 미리 알고 있으면,

시행착오를 크게 줄일 수 있습니다.

4. 실무에서 겪는 함정과 해결 방법

UVM을 배울 때 누구나 겪는 전형적인 실수들과 그 해결책을 상세히 다룹니다.

다루는 주요 이슈들:

config_db에서 virtual interface를 가져오지 못하는 경우 (scope와 instance path 문제)

Phase 순서를 잘못 이해해서 object가 null이 되는 경우

TLM port 연결 시 방향을 반대로 하는 실수

Objection을 raise하지 않아 시뮬레이션이 즉시 종료되는 문제

Sequence와 Driver 간의 handshake 오류

Factory override가 적용되지 않는 경우의 원인

각 이슈에 대해:

증상: 어떤 에러 메시지나 동작이 나타나는가?

원인: 왜 이런 문제가 발생하는가?

해결: 어떻게 고쳐야 하는가?

예방: 처음부터 이런 실수를 피하는 방법

이는 독학으로 수개월씩 시행착오를 겪을 내용을 미리 정리하여,

학습 시간을 획기적으로 단축시켜줍니다.

그런데 실수를 예방하는 것만큼 중요한 것이 하나 더 있습니다.

문제가 생겼을 때 빠르게 찾아내고 해결하는 능력입니다.

바로 이것이 Reporting Mechanism을 첫 챕터에서 다루는 이유입니다.

5. 디버깅 도구로서의 Reporting Mechanism

많은 UVM 교재가 Reporting을 마지막에 간단히 다루거나 아예 생략합니다.

하지만 실무에서는 디버깅 능력이 코딩 능력만큼 중요합니다.

이 핸드북은 첫 챕터에서 UVM Reporting Mechanism을 상세히 다룹니다:

기본 Reporting Macros (

uvm_info,uvm_warning,uvm_error,uvm_fatal)Verbosity Level을 통한 메시지 필터링

ID 기반 선택적 메시지 제어

Component별 독립적 Reporting 관

리

Severity Override를 통한 런타임 동작 변경

File 기반 Logging

이를 먼저 배움으로써, 이후 모든 학습 과정에서 코드가 어떻게 동작하는지 추적할 수 있습니다.

복잡한 UVM 환경에서 문제를 빠르게 찾아내는 능력은 현업에서 가장 중요한 스킬 중 하나입니다.

퀴즈와 실습 과제

각 챕터마다 포함:

개념 확인 퀴즈

: 핵심 개념 점검

코드 분석 문제: 주어진 UVM 코드의 동작 예측

디버깅 문제: 잘못된 코드를 찾아 수정하기

설계 문제: 요구사항에 맞는 검증 환경 설계하기

이런 분들께 강력히 추천합니다!

취업 준비생

✅ SystemVerilog Testbench를 작성할 수 있지만, 실무 프로젝트 경험이 부족한 분

✅ 이력서와 포트폴리오에 UVM 프로젝트를 추가하고 싶은 분

✅ 면접에서 UVM 관련 질문에 자신 있게 답변하고 싶은 분

✅ 글로벌 반도체 기업(삼성, SK하이닉스, TSMC, Intel, NVIDIA 등)의 검증 엔지니어를 목표로 하는 분

현업 엔지니어

✅ 현업에서 UVM을 사용하고 있지만, 깊은 이해 없이 기존 코드를 수정하는 수준인 분

✅ 검증 환경을 처음부터 설계해야 하는데 어디서부터 시작해야 할지 막막한 분

✅ 팀에서 재사용 가능한 VIP를 개발하고 관리해야 하는 분

✅ 검증 팀 리더로서 표준화된 방법론을 도입하고 싶은 분

학생 및 연구자

✅ 논문이나 프로젝트에서 복잡한 하드웨어를 체계적으로 검증해야 하는 분

✅ 학부나 대학원에서 UVM을 배우고 싶지만 적절한 교재가 없는 분

학습 후 얻을 수 있는 구체적인 역량

이 핸드북을 완료하면 무엇이 달라질까요?

막연한 기대가 아닌, 구체적이고 측정 가능한 역량을 얻게 됩니다.

기술적 역량

🎯 완전한 UVM 검증 환경을 설계하고 구현할 수 있는 능력

🎯 재사용 가능한 UVM VIP를 개발하고 관리하는 능력

🎯 복잡한 프로토콜과 IP를 체계적으로 검증하는 실무 역량

🎯 Phase, TLM, Sequence의 동작 원리를 깊이 있게 이해

🎯 디버깅 전략을 수립하고 빠르게 문제를 해결하는 능력

경력 개발

🎯 이력서와 포트폴리오에 UVM 프로젝트를 추가 (GitHub 등)

🎯 면접에서의 경쟁력 향상 (UVM 관련 질문에 정확한 답변 가능)

🎯 연봉 협상에서 강력한 무기 (희소성 높은 기술 보유)

🎯 팀 내 영향력 증대 (검증 방법론 전문가로 인정)

🎯 경력 성장 경로 확보 (검증 리더, 아키텍트로의 발전)