한 권으로 끝내는 System Verilog Verification 실무 핸드북

2025. 09. 24. 18:52

수정됨

한 권으로 끝내는 System Verilog Verification 실무 핸드북.zip

62.4MB

7개의 챕터 中 1챕터를 무료 공개합니다.

→ 1챕터 다운받기(Click!)

💻 취업 준비 + 현업에서 필요할때마다 꺼내 쓰세요.

왜 Verification인가? RTL 설계의 함정

대학이나 대학원에서 디지털 회로나 SoC 설계를 배워본 분들은 많습니다.

RTL로 CPU 설계, NPU 설계…

누구나 한 번쯤은 “멋진 칩을 직접 만들어보고 싶다”는 꿈을 꿉니다.

하지만 현실은 조금 다릅니다.

반도체 산업의 70% 이상 인력이 ‘검증(Verification)’에 투입되고 있다는 사실, 알고 계셨나요?

칩 하나가 Tape-out에 실패하면 수십억 원의 손실이 발생하기 때문에,

설계만큼이나 철저한 검증 환경 구축이 절대적으로 중요해지고 있습니다.

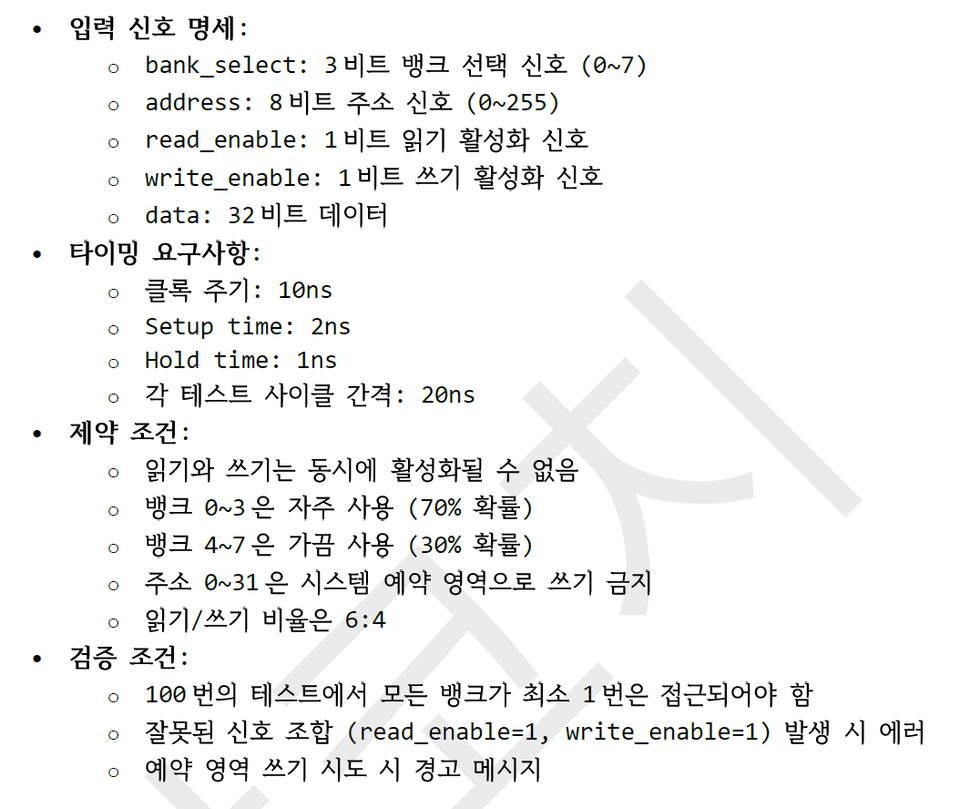

반도체 칩 설계의 복잡성은 매년 58%씩 증가하지만, 생산성은 21% 증가에 그칩니다.

위 그래프에서 보이듯, 두 곡선 사이에는 점점 커지는 Design Gap이 존재합니다.

이 갭을 메우기 위해 산업계가 선택한 방법이 바로 IP 재사용과 철저한 Verification입니다.

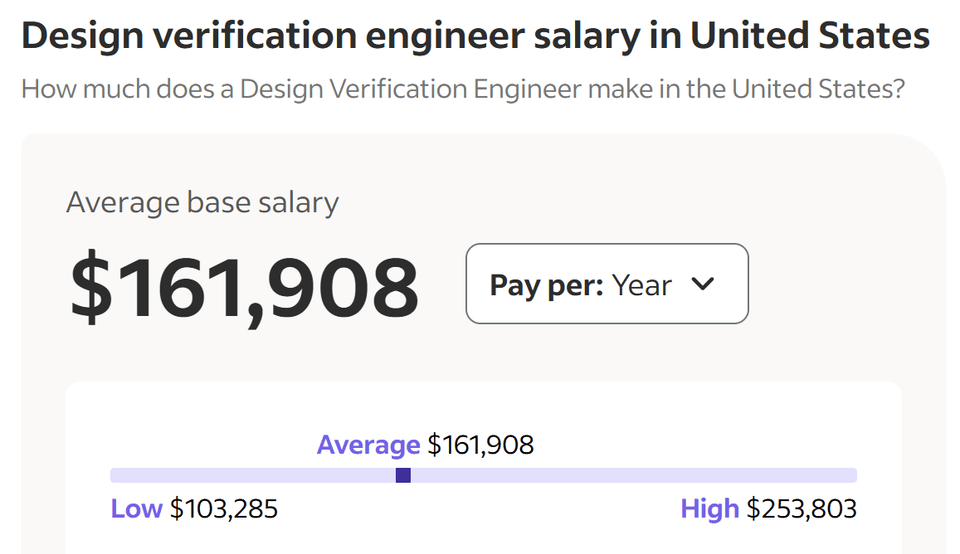

Verification 엔지니어의 가치(연봉)

Verification은 단순히 “테스트하는 직무”가 아닙니다.

칩의 품질, 테이프아웃 성공 여부, 나아가 수십억 달러 프로젝트의 성패를 결정짓는 핵심 분야입니다.

그만큼 보상도 다릅니다.

미국에서 Design Verification Engineer의 평균 연봉은 $161,908 (약 2억 원)에 달하며,

경력자라면 25만 달러(약 3억 원) 이상을 받기도 합니다.

하지만 막상 배워보면 어렵습니다.

RTL 설계 지식만으로는 현업에서 곧바로 Verification 업무를 수행하기 어렵습니다.

Testbench, OOP, Randomization, IPC, Interface 같은 실무 기술이 필수이지만,

학교에서는 잘 다루지 않기 때문입니다.

이 핸드북은 바로 그 갭을 메워줍니다.

1. 체계적이고 산업 친화적인 커리큘럼

이 핸드북은 단순히 문법을 나열하는 수준을 넘어서,

실제 Verification 엔지니어가 성장하는 흐름을 그대로 따라갈 수 있도록 설계되었습니다.

기초 절차적 구문(Procedural Constructs)과 데이터 타입 이해에서 출발해,

검증의 근본 개념(Verification Fundamentals)을 다지고,

객체지향(OOP), Randomization, IPC, Interface 등 실무에서 반드시 마주치는 기술로 확장됩니다.

즉, 학교에서 배우는 RTL 설계 지식을 가진 학습자가 “현업 검증 엔지니어”로 자연스럽게 이어질 수 있도록,

기초 → 심화 → 실무 적용의 단계별 학습 경로를 제공합니다.

(SystemVerilog 학습 목차)

1. Fundamentals Procedural Constructs → 무료 공개

하드웨어 설계에서 Procedural Programming이 왜 필요한가

Testbench의 본질과 Signal Types 심화 이해

Initial Block: 시뮬레이션 시작의 모든 것

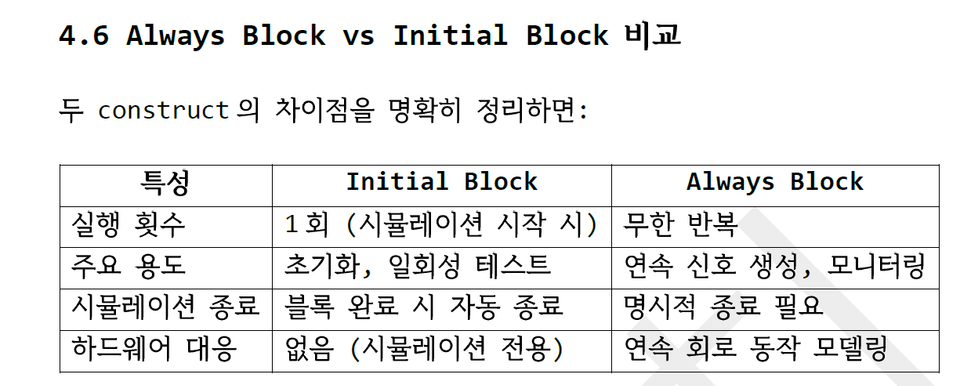

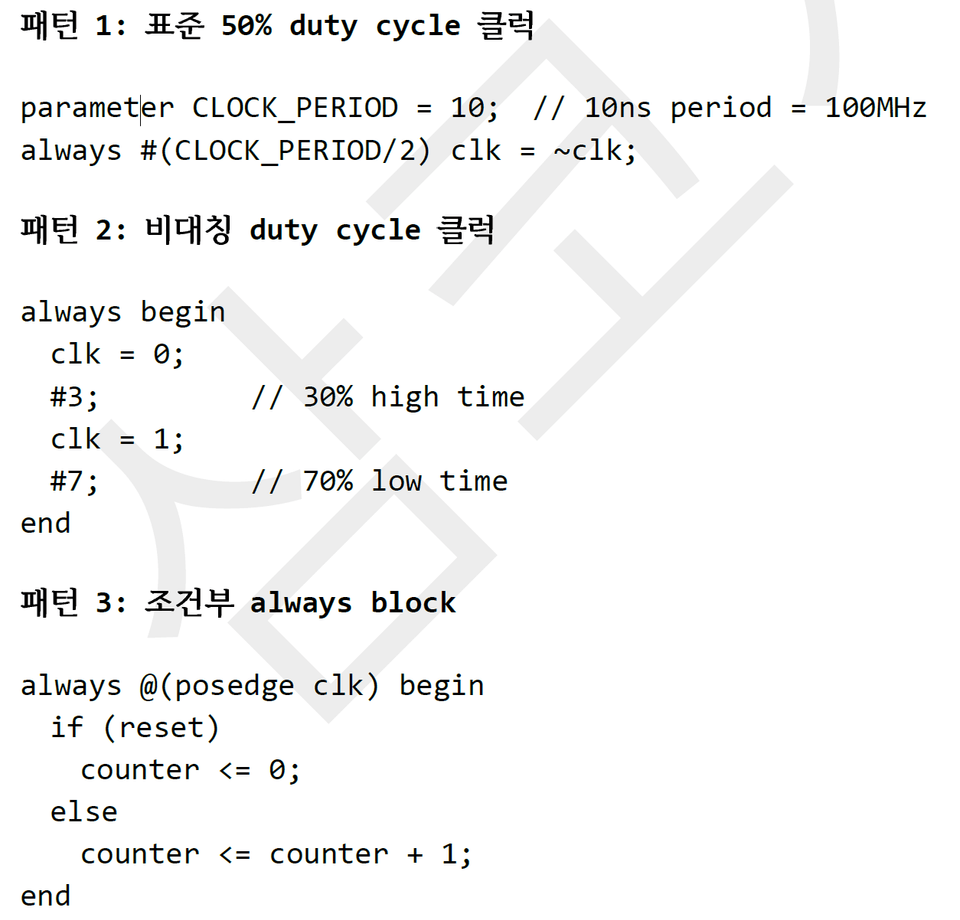

Always Block: 연속 동작과 Clock의 하드웨어 구현

Timescale: 시간 해상도가 시뮬레이션에 미치는 영향

Task를 활용한 매개변수화된 Clock 생성

실제 프로젝트에서의 적용과 함정 회피

2. Understanding SV Datatypes

Array가 왜 필요한가 - 근본적 이해

SystemVerilog Array의 내부 구조 파헤치기

변수 선언의 숨겨진 의미

For Loop 초기화 - 전통적 방법의 깊이있는 이해

Foreach Loop 초기화 - 현대적 방법의 장점과 한계

Repeat문 초기화 - 단순함 뒤의 복잡한 제어

세 방법의 심화 비교와 선택 기준

Array 출력 포맷의 비밀

하드웨어 구현 관점

흔히 저지르는 실수들과 해결책

3. SystemVerilog Verification Fundamentals

검증(Verification)이란 무엇인가?

Verification Plan의 이해

Test 방법론 비교

Testbench Architecture

Testbench Components 상세 분석

실무 검증 프로세스

4. Fundamentals of SystemVerilog OOP Construct

객체지향 프로그래밍이란 무엇인가요?

Class의 기본 개념 이해하기

Class에 기능 추가하기: Method의 세계

생성자(Constructor)로 객체 초기화하기

Class 안에 Class 넣기: 복합 객체

객체 복사하기: Shallow Copy vs Deep Copy

상속과 다형성: 코드 재사용의 극치

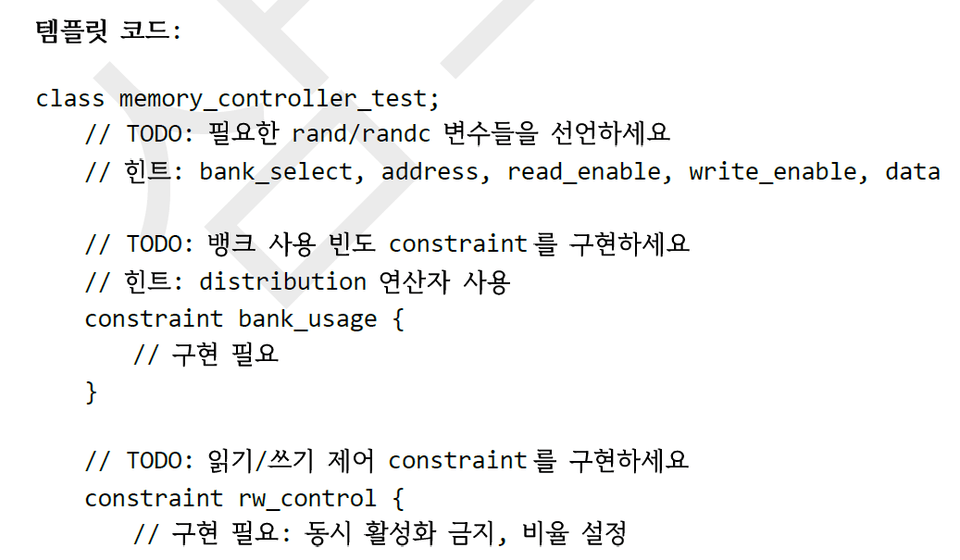

5. Randomization

왜 Randomization을 배워야 할까요?

첫 걸음: 기본 Random 값 생성하기

rand vs randc: 두 가지 무작위의 차이점

Randomization 실패를 대비하는 방법

Multiple Stimuli와 객체 생성 타이밍

Constraint: 원하는 범위로 제한하기

External Function과 Constraint 분리하기

Pre/Post Randomization: 전처리와 후처리

Weighted Distribution: 확률에 가중치 주기

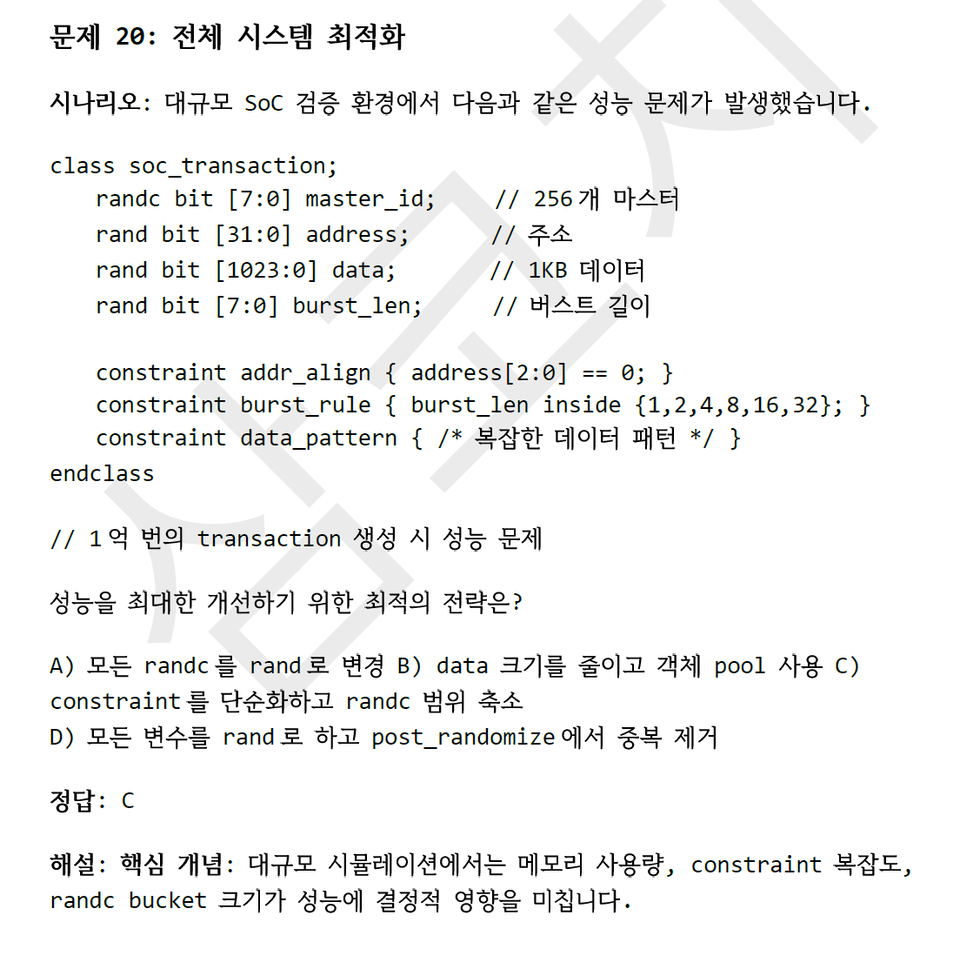

고급 Constraint 연산자들

Constraint 제어 기법 (constraint_mode)

6. IPC (Interprocess Communication)

IPC의 근본적 필요성과 하드웨어 시뮬레이션의 특성

Event 메커니즘 - 프로세스 간 신호 전달

Multiple Process의 실행과 동기화 문제

FORK JOIN 구문 - 병렬 실행 제어의 핵심

Semaphore - 공유 자원 접근 제어 메커니즘

Mailbox - 프로세스 간 데이터 전송 시스템

실무 적용과 흔한 오류 패턴

7. Getting Started with Interface

왜 Interface가 필요할까요?

Interface 기본 개념과 구현

Interface에서의 연산자 선택

LOGIC vs WIRE/REG in Interface

Driver 클래스와 Interface

MODPORT의 이해

Generator와 Mailbox 시스템

상속과 오류 주입

Monitor와 Scoreboard 구현

실무 활용 가이드와 팁

2. 현업에서 바로 적용 가능한 코드 예제

이 핸드북은 단순한 이론 설명에 그치지 않습니다.

각 개념마다 SystemVerilog 예제 코드를 함께 제시하고, 코드의 동작 원리와 설계 의도를 단계별로 분석합니다.

예를 들어,

Event, Semaphore, Mailbox 같은 IPC 메커니즘은 실제 동기화 시나리오 코드와 함께 동작 과정을 시각적으로 설명하고,

Driver, Monitor, Scoreboard 같은 검증 컴포넌트는 클래스 정의부터 실행 플로우 다이어그램까지 제공하여 실제 Testbench 설계 패턴을 익힐 수 있습니다.

즉, 단순히 문법을 아는 것을 넘어, 실무 환경에서 그대로 가져다 쓸 수 있는 코드 자산과 설계 감각을 함께 얻을 수 있습니다.

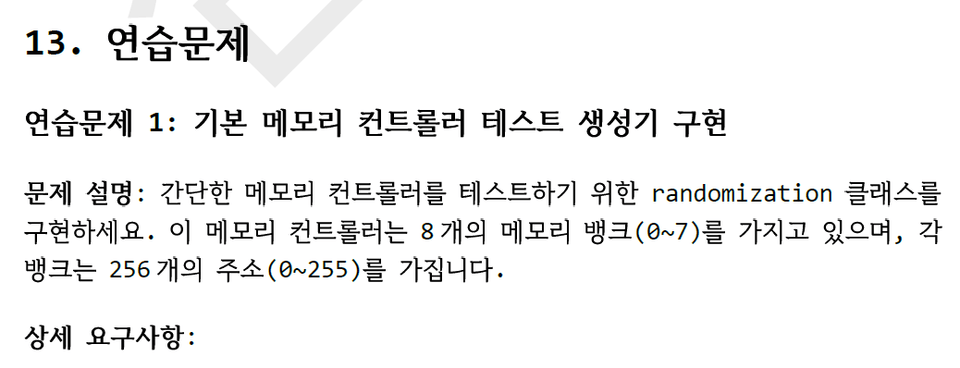

3. 검증 역량을 다지는 퀴즈와 실습 과제

핸드북에는 단순 이론 확인용 문제가 아니라, 실무 시나리오 기반의 퀴즈와 과제가 포함되어 있습니다.

각 장의 핵심 개념을 점검할 수 있는 퀴즈(20문항)는 학습자가 놓치기 쉬운 포인트를 되짚어 주며,

실습 과제는 CPU 명령어 검증, 패킷 처리 파이프라인, 복잡한 Monitor와 Protocol Checker 설계 등 실제 프로젝트 상황을 재현합니다.

이를 통해 독자는 단순히 “이론을 이해했다”에서 그치지 않고,

스스로 검증 환경을 설계하고 문제를 해결하는 능력을 훈련할 수 있습니다.

즉, 이 핸드북은 지식을 전달하는 데서 멈추지 않고, 학습자가 실무 엔지니어로 성장할 수 있는 실질적 훈련 도구가 됩니다.

4. 표준 기반의 정확성과 신뢰성

이 핸드북은 단순히 경험이나 관습적 설명에 의존하지 않습니다.

모든 주요 주제는 IEEE 1800-2017 SystemVerilog Language Reference Manual (LRM)과 연결되어 있으며,

각 기능(Event, Semaphore, Mailbox, Fork-Join, Process Management 등)에 대응하는 LRM 섹션을 명확히 제시합니다.

덕분에 단순히 “어떻게 쓰는지”를 넘어,

왜 그렇게 정의되었는지, 어떤 제약과 규칙이 있는지를 표준 문서에 근거해 확인할 수 있습니다.

이는 현업에서 종종 요구되는 표준 준수 검증(Compliance Verification)이나 팀 내 코드 리뷰 상황에서도 강력한 무기가 됩니다.

즉, 이 핸드북은 학습 자료를 넘어 표준 기반의 레퍼런스 가이드로서,

실무자가 신뢰할 수 있는 검증 지식의 기준점을 제공합니다.