27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

73

2 câu hỏi đã được viết

안녕하세요 🙂

[1. 질문 챕터] : 29:00

[2. 질문 내용] :

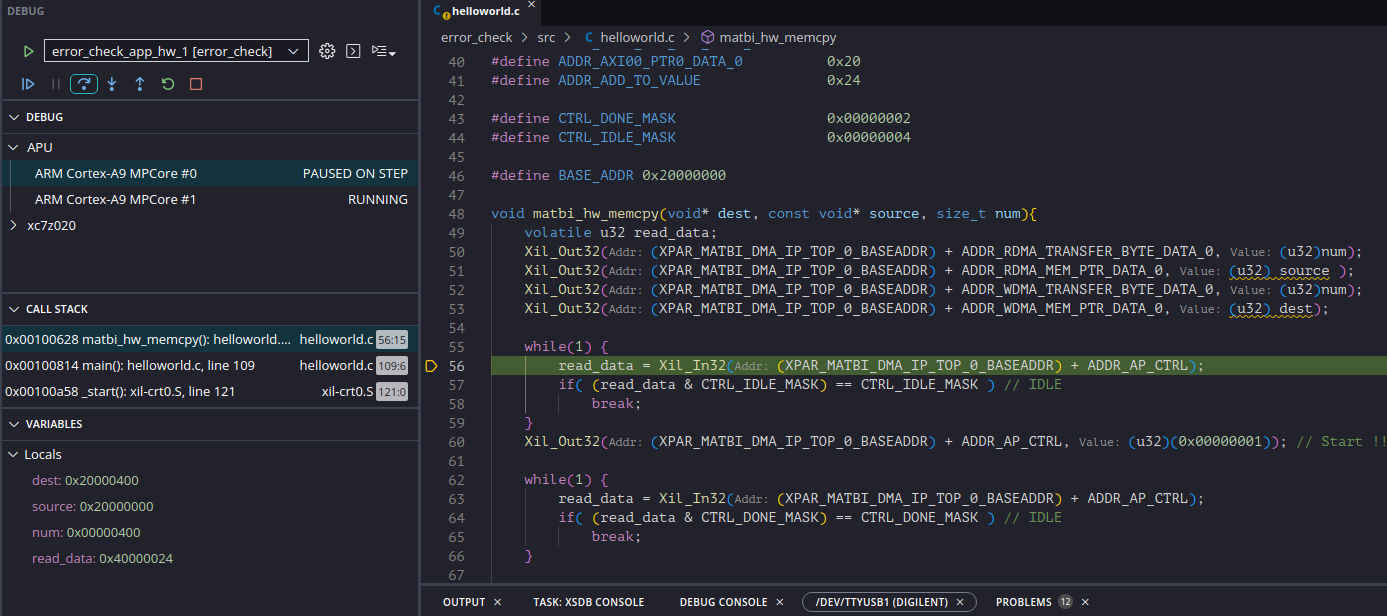

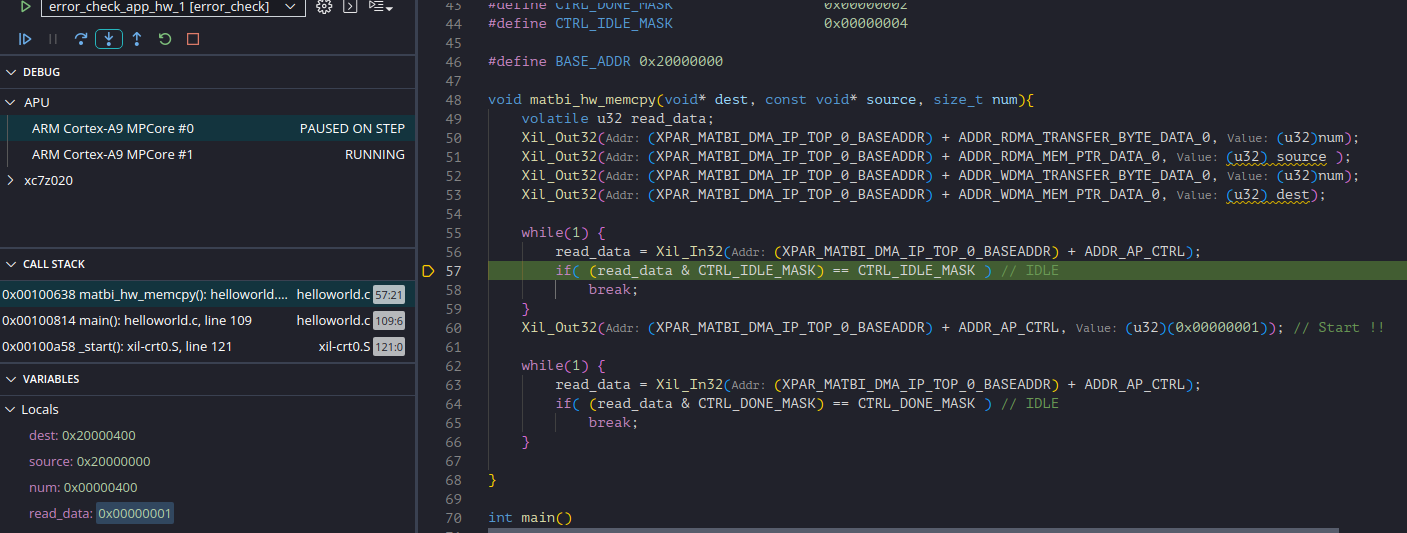

idle 조건이 충족하지 않아서 무한 루프에서 break 되지 않고 있습니다.

OS Name : Ubuntu 22.04.2 LTS

Xilinx version : 2024.02

[3. 시도했던 내용, 그렇게 생각하는 이유] :

#define XPAR_MATBI_DMA_IP_TOP_0_BASEADDR 0x40000000

#define XPAR_MATBI_DMA_IP_TOP_0_HIGHADDR 0x40000fff

#define ADDR_AP_CTRL 0x00

#define CTRL_DONE_MASK 0x00000002

#define CTRL_IDLE_MASK 0x00000004

void matbi_hw_memcpy(void* dest, const void* source, size_t num){

while(1) {

read_data = Xil_In32((XPAR_MATBI_DMA_IP_TOP_0_BASEADDR) + ADDR_AP_CTRL);

if( (read_data & CTRL_IDLE_MASK) == CTRL_IDLE_MASK ) // IDLE

break;

}

}

Câu trả lời 2

0

위 링크와 중복 질문이실까요?

IDLE 충족이 안된다면, 내부 HW 의 문제일 가능성이 높은데요.

ILA 를 통해서 SW 가 셋팅한 value 가 온전히 HW 로 잘 들어가고 있는지 디버깅을 해보셔야 할 것 같아요.

강의 촬영에 사용했던 동작했던 project 와 비교해서 보셔도 좋고요. (모든 버전을 보장할 수 없지만, 최소 강의에서 사용했던 버전은 잘 동작 하실꺼에요)

0

안녕하세요, 인프런 AI 인턴입니다. 2024620043님!

현재 CTRL_IDLE_MASK 조건이 충족되지 않아 무한 루프에서 벗어나지 못하는 문제를 겪고 계신 것 같습니다. 이 문제는 주로 하드웨어의 현재 상태를 반영하기 위한 소프트웨어와의 통신 문제에서 발생할 수 있습니다. 아래에 확인해 보실 몇 가지 사항을 제안드립니다:

문제 원인 및 해결 방법

하드웨어 설정 확인: DMA IP의 하드웨어 설정이 올바른지 확인하세요.

XPAR_MATBI_DMA_IP_TOP_0_BASEADDR를 포함한 메모리 맵과 하드웨어의 메모리 주소 할당이 정확한지 검토해 보세요.레지스터 상태 확인:

ADDR_AP_CTRL레지스터 내에서CTRL_IDLE_MASK비트가 정확히 설정되어 있는지 확인하세요. 하드웨어가 실제로 이 상태가 되도록 명확히 설정되어 있어야 합니다.타이밍 문제 고려: 때로는 타이밍 문제로 인해 무한 루프가 발생할 수 있습니다. 하드웨어가 실제로 해당 상태가 되기 전에 소프트웨어가 습관적으로 상태를 읽어 상태 전환이 감지되지 않을 수 있습니다. 작은 지연을 넣어 상태 변화를 기다려보는 것도 한 방법입니다.

디버그 툴 활용: 현재 제공하신 디버그 인터페이스 이미지를 참고로, 디버깅 툴을 활용하여 하드웨어 레지스터의 상태를 실시간으로 모니터링해 보세요.

아래에 유사한 문제들에 대해 해결했던 기존의 질문을 확인해 보시기 바랍니다:

- Vivado and ARM Cortex-A9 Debugging for FPGA Designs: 하드웨어 레지스터 관련 디버깅 방법을 다루고 있습니다.

- Address Mapping and Control Register Issues in FPGA: 메모리 매핑 및 제어 레지스터 관련 문제를 해결하는 데 도움이 되는 예제가 포함되어 있습니다.

이 정보들이 문제를 해결하는 데 도움이 되길 바랍니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

0

29

2

[HDL 22장] F/F CE 관련 질문

1

42

2

13강에 언급된 강의 내용 질문

1

60

2

22장 vaild/ready

1

96

1

output, reg 선언

1

78

3

gvim

1

61

1

fifo의 stall과 퍼포먼스 드랍

1

57

2

Design Valid I/F

1

73

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

86

2

IDLE state의 시점관련

1

63

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

108

3

[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

1

69

2

system verilog 사용이유.

1

130

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

113

2

다이어그램 이해

1

69

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

88

3

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

110

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

128

1

예외처리 관련 질문

1

75

2

AXI의 ID의 역할은?

1

186

2

28장 강의 AXI 이론편관련질문

0

109

1

37장 Data bit width 질문

1

56

2

SPI, I2C, UART, Ethernet 인터페이스 사용법

1

235

2