27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

88

2 câu hỏi đã được viết

[1. 질문 챕터] :

29:00

[2. 질문 내용] :

질문 : BASE_ADDR의 Addr read exception.

OS Name : Ubuntu 22.04.2 LTS

Xilinx version : 2024.02

[3. 시도했던 내용, 그렇게 생각하는 이유] :

전체 코드 :

#define AXI_DATA_BYTE 8 // 64 / 8

#define BASE_ADDR 0x10000000

int main()

{

init_platform();

Xil_DCacheEnable();

Xil_ICacheEnable();

u32 transfer_cnt;

u32 add_val;

while (1)

{

printf("======= Verilog Season2 matbi_mem_copy_test ======\n");

do{

printf("plz input transfer_cnt\n");

scanf("%u",&transfer_cnt);

}while( !( (0 < transfer_cnt) && (transfer_cnt%AXI_DATA_BYTE == 0) && (transfer_cnt <= 67108864) ) ); // 64 *(2^20) = 64 MBytes // max count 32-6 = 26. 2^26 = 64MBytes

do{

printf("plz input add_val (0~255)\n");

scanf("%u",&add_val);

}while( !( (0 <= add_val) && (add_val<256) ) );

u8* rdma_baseaddr = (u8*)BASE_ADDR;

volatile u8 data = Xil_In8(rdma_baseaddr);

}

cleanup_platform();

return 0;

}

오류 발생 :

xil_io.h 파일

static INLINE u8 Xil_In8(UINTPTR Addr)

{

return (volatile u8 ) Addr;

}

xil_exception.c 파일

static void Xil_DataAbortHandler(void *CallBackRef)

{

xdbg_printf(XDBG_DEBUG_GENERAL, "Address of Instruction causing Data abort %lx\n",DataAbortAddr); // 0x00100588

while(1)

{

}

}

원인 ? :

여기서 무엇을 진행해야 할까요?

Câu trả lời 3

0

아.. 이해했습니다.

전달드린 코드 수정 없이, 영상까지 따라하셨는데 문제가 있으신 거군요.

현실적으로 디버깅을 대신 해드린다는건 말이 안되서, 실습파일을 보시면, 프로젝트를 통째로 압축해서 드리고 있는데요. 2022.2 에서 해보시면 가장 좋을 것 같아요.

2024.2 에서 어떤일이 벌어지고 있는지 파악하기에는 어려워서,

몇 가지 확인해보라고 하고 싶은 부분을 말씀드리면

BASE_ADDR 을 수정해보기.

0x10000000 번지면, Zybo board 의 1GB 영역에서 25% 해당하는 구간이라. (큰 기대는 안하지만..) 혹시나 겹칠 수 있으니, 0x10000000 -> 0x20000000 도 해보시고 값을 변경해보시면 좋을 것 같아요.ILA 를 이용하여 각 SW 코드의 line by line 에 HW 의 명령어가 정상적으로 전달되는지 확인. 시간은 오래 걸리지만 가장 확실한 방법입니다. 정석 디버깅 입니다.

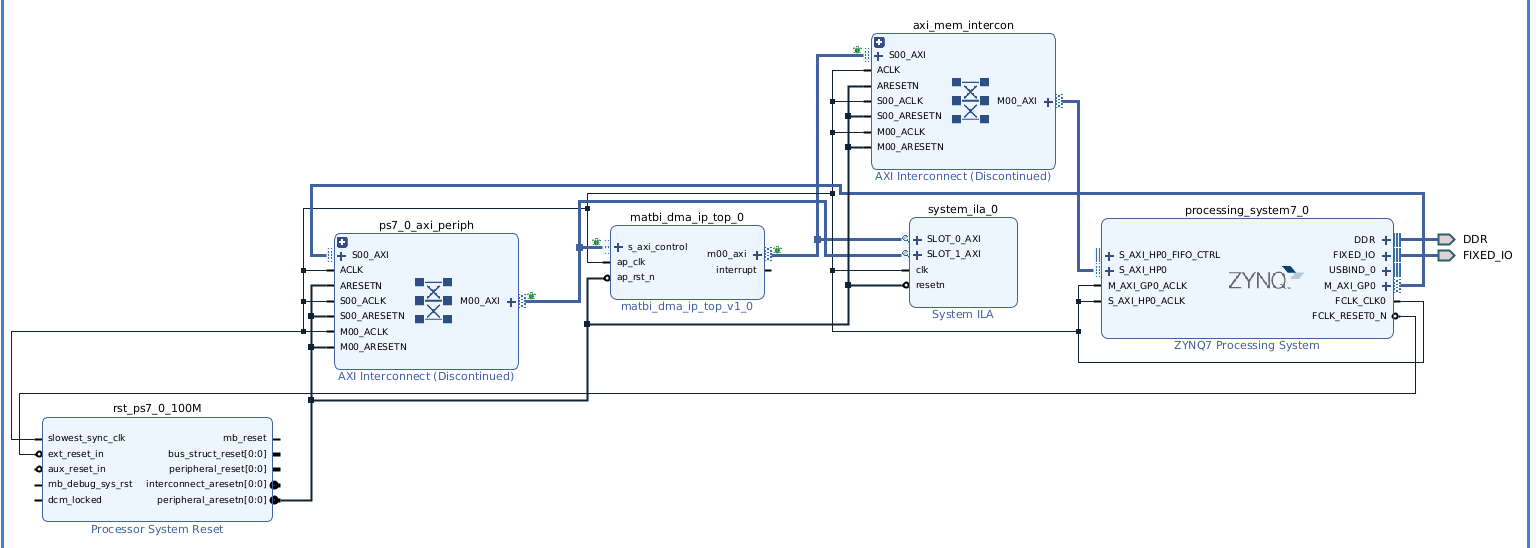

FPGA 시간에 ILA 사용방법을 다룬 적이 있고요. HW 의 실제 동작의 waveform 을 dump 하여 눈으로 볼 수 있는 기능입니다. 이것과 SW 의 break point 를 조합해서 내가 주고있는 command 가 잘 가고 있구나 눈으로 직접 보시면서 step by step 으로 가시면 되겠습니다.

즐공하세요!

1

답변 감사합니다.

Xil_DataAbortHandler 무한 루프 문제는 말씀하여 주신 1번으로 해결되었습니다.

2번은 "28. [프로젝트-2] Mem copy IP 의 Performance 분석하기"에서 설명되는 아래 사진을 말씀하시는 건가요?

0

안녕하세요 🙂

질문이 잘 이해가 안되는데요.

전달드린 실습코드 자체에 문제가 있는걸까요? 아니면 수정을 하신 걸까요?

1

안녕하세요

제공하여 주신 SW폴더에서 matbi_mem_copy_test.c를 z7-20에 적용하고

scanf에 해당되는 1024 하고 0을 입력하면 Xil_DataAbortHandler 함수의 무한 루프에 있습니다.

코드 수정하면서 확인하고 있는데 아래 코드에서 문제가 발생하는 것 같습니다.

43 line → #define BASE_ADDR 0x10000000

85 line → u8* rdma_baseaddr = (u8*) BASE_ADDR;

91 line → rdma_baseaddr[addr] = data;

0

안녕하세요, 인프런 AI 인턴입니다. 2024620043님!

BASE_ADDR의 Addr read exception 문제에 대해 고민하고 계시는군요. 주어진 상황에서는 BASE_ADDR에 접근하는 과정에서 발생하는 오류일 가능성이 높습니다. 아래의 몇 가지 사항을 확인해 보시기 바랍니다.

문제 원인 및 해결 방법

메모리 맵핑 확인: 주어진

BASE_ADDR(0x10000000)이 실제 구현된 하드웨어의 메모리 맵에서 올바른 주소인지 확인하세요. 사용하려는 메모리 공간이 해당 주소 범위에서 존재하지 않는다면 접근 오류가 발생할 수 있습니다. VIvado에서 주소 공간을 할당했는지 확인해 보세요.Xil_In8 함수를 통한 데이터 읽기 방법 재검토:

Xil_In8함수에서 반환되는Addr는 8비트 데이터로 캐스팅됩니다. 하드웨어 구현이 8비트 읽기에 적합한지 확인하시고, 필요에 따라 데이터 폭을 조정하세요.권한 설정 및 접근 가능성: 만약 이 주소가 외부 메모리에 할당되어있는 것이라면, DDR 컨트롤러나 AXI 인터페이스 설정이 제대로 되었는지 확인하세요. 권한 문제가 발생할 수 있습니다.

디버그 정보 활용: 오류 발생 시

xil_exception.c의Xil_DataAbortHandler에서 발생한 주소(DataAbortAddr)를 활용하여 어떤 주소에서 문제가 발생했는지 확인하고, 해당 주소의 메모리 맵 및 하드웨어 설정이 올바른지 검토하세요.

관련하여 문제 해결에 도움이 되는 유사한 질문을 확인해 보시기 바랍니다:

- Address Mapping in FPGA Design and Troubleshooting: 주소 매핑 및 해당 영역의 문제를 해결하는 방법에 대해 설명합니다.

- Vivado Address Configuration Issues and Debugging: Vivado의 주소 설정 시 발생하는 문제와 해결 방법을 다루고 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

0

29

2

[HDL 22장] F/F CE 관련 질문

1

42

2

13강에 언급된 강의 내용 질문

1

60

2

22장 vaild/ready

1

96

1

output, reg 선언

1

78

3

gvim

1

61

1

fifo의 stall과 퍼포먼스 드랍

1

57

2

Design Valid I/F

1

73

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

86

2

IDLE state의 시점관련

1

63

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

108

3

[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

1

69

2

system verilog 사용이유.

1

130

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

113

2

다이어그램 이해

1

69

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

73

2

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

110

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

128

1

예외처리 관련 질문

1

75

2

AXI의 ID의 역할은?

1

186

2

28장 강의 AXI 이론편관련질문

0

109

1

37장 Data bit width 질문

1

56

2

SPI, I2C, UART, Ethernet 인터페이스 사용법

1

235

2