안녕하세요 I2C Register 모듈에 대해서 질문이있습니다.

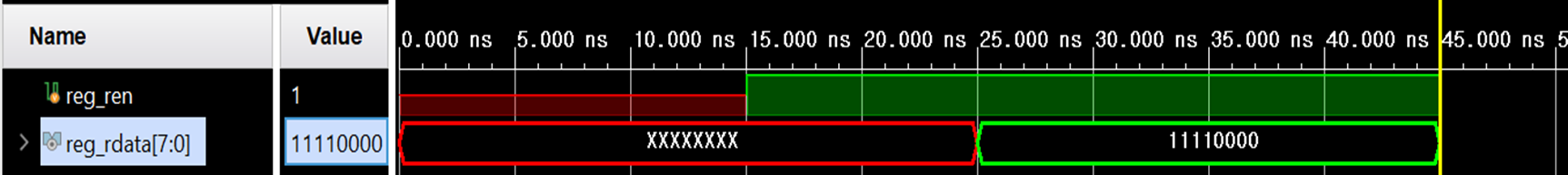

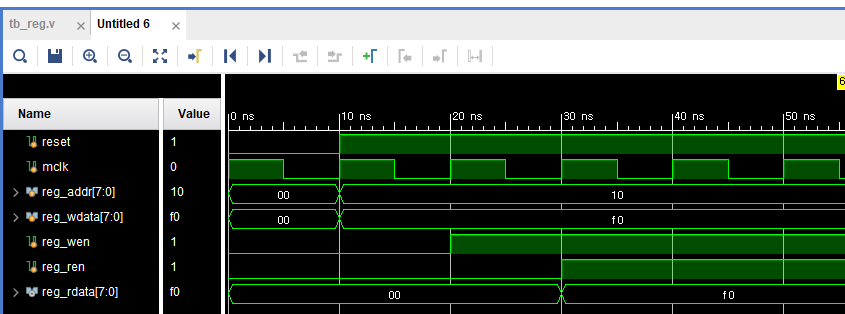

이 부분에서 reg_ren이 1일때 reg10에 저장된 값을 읽으려하는데 저의 생각에는 reg_ren값이 1이 되는 순간 reg_rdata값이 나올줄 알았는데 5ns뒤인 20ns뒤에 나오는걸 확인했습니다.

이 부분에서 reg_ren이 1일때 reg10에 저장된 값을 읽으려하는데 저의 생각에는 reg_ren값이 1이 되는 순간 reg_rdata값이 나올줄 알았는데 5ns뒤인 20ns뒤에 나오는걸 확인했습니다.

이런 타임딜레이는 하드웨어상 어쩔수없는 딜레이인가요?

回答 1

1

문서의 어떤 부분인지 알려주시면(페이지) 감사하겠습니다.

일단 파형으로 봐서는 simulation이 시작되는 부분이네요.

해당 모듈의 reset, mclk (main clock)이 어떤지 확인해 보시고요,

reg_ren 신호를 어떻게 만드셨는지요?

모든 코드들은 mclk (main clock)과 동기되어 동작하도록 되어 있어서, mclk와 같이 파형을 보셔야 합니다.

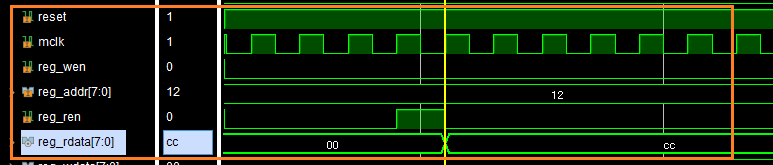

아래는 tb_i2c_slave8x8 simulation 파형입니다. reg_ren이 Active 되고 그 다음 mclk clock에 reg_rdata가 나오도록 동작합니다.

0

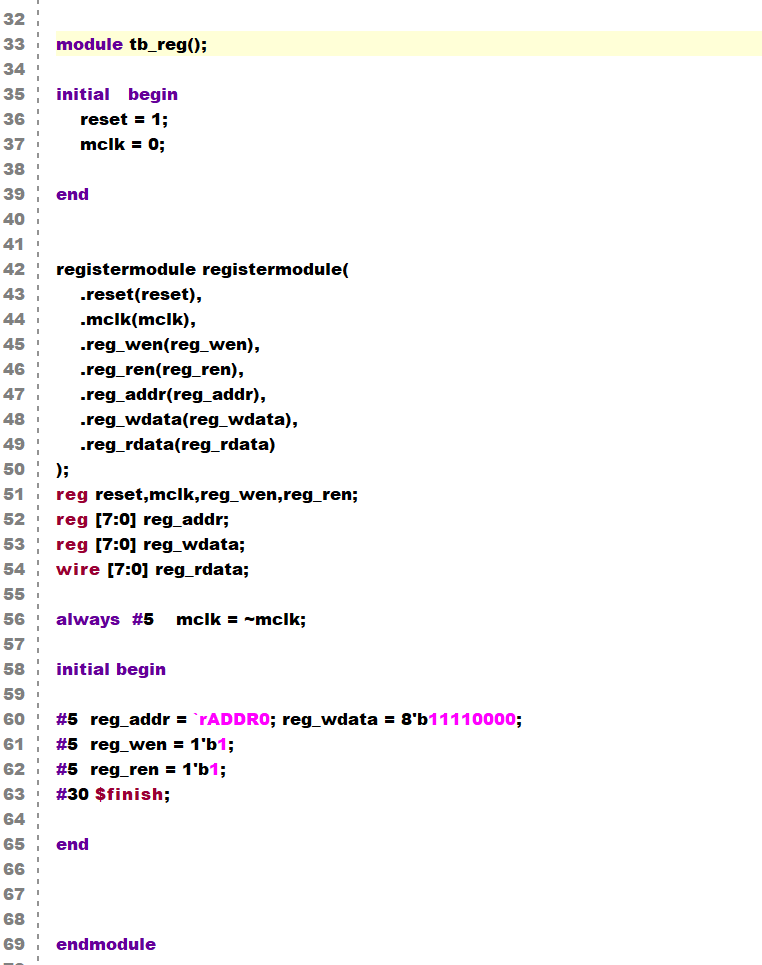

fpga_intro에 있는 reg 8*8부분(11.3.3, 192page)만 따로 모듈화하여 테스트벤치 해보았습니다.

이건 제가 구성한 테스트벤치 코드입니다! 제가 궁금한건 reg_rdata가 reg_ren이 입력되는 동시에 값이 읽혀야 하는건지 궁금하여 여쭤봅니다.

이건 제가 구성한 테스트벤치 코드입니다! 제가 궁금한건 reg_rdata가 reg_ren이 입력되는 동시에 값이 읽혀야 하는건지 궁금하여 여쭤봅니다.

0

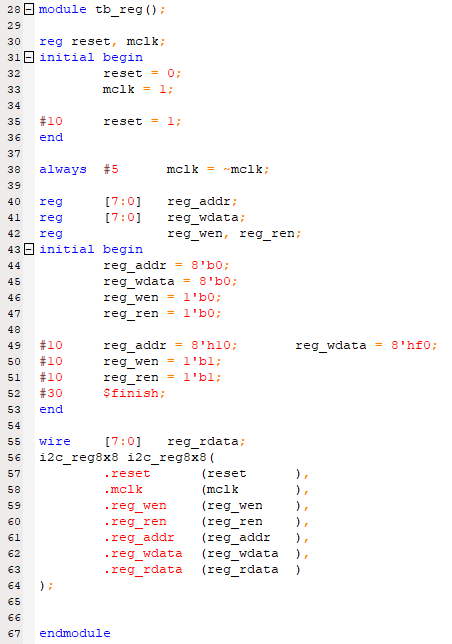

registermodule 로 구성된 모듈(강의의 소스는 i2c_reg8x8 입니다만)의 read/write 동작은 mclk의 positive edge에서 동작합니다.

작성하신 test bench의 mclk 주기가 2x5ns = 10ns 입니다.

read/write 동작이 완료되기 위해서는 적어도 10ns 의 시간이 필요합니다.

작성하신 test bench에서는 5ns 단위로 동작합니다. 이는 read/write 동작을 위한 시간이 부족하게 됩니다.

#5 을 #10으로 변경해서 테스트 해보시길 바랍니다.

그리고 simulation 하면 오류 발생하지 않나요?

모든 신호들은 reg, wire 선언후 사용해야 맞는 것입니다.

아래 코드는 제가 수정해서 simulation 한 코드입니다.

참고하시길 바랍니다.

simulation 결과입니다.

[HDL 32장-2부] 참고 링크 관련

1

36

2

강의 만료일 연장 신청

0

33

2

기초예제 파일 불러오기 문의

0

26

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

31

2

Verilog 코딩 스타일

0

119

2

xilinx 권고와 차이

0

248

2

강의자료

0

115

1

open hardware manager에서 보드 인식 못하는 문제

0

345

2

ifelse, 삼항연산자에 대해서 질문 있습니다.

0

425

1

RAM ip를 이용하여 FIFO 기능을 구현할 수도 있나요?

0

327

1

SPI MASTER 질문

0

248

1

SPI master testbench 질문

0

327

1

자사 개발보드 관련

0

357

2

안녕하세요. IP Packaging 관련 질문 있습니다.

0

317

1

안녕하세요. verilog 활용 관련 문의드립니다.

0

342

1

안녕하세요 fpga_intro_v16 192p에 질문있습니다!

0

336

1

안녕하세요 SLVAE 컨트롤러에 대한 질문이 있습니다

0

371

1

SPI에서 Master 내의 miso 값 update 과정에서 질문있습니다.

1

878

1

안녕하세요 i2c master 부분에 관련하여 질문있습니다.

0

612

1

SPI Master 부분 질문입니다.

1

612

3

I2C Master 모듈관련 질문입니다.

0

1182

1

memory configuration

0

841

1

UART, SPI구현

0

657

1

SPI와 I2C의 차이

2

1981

1