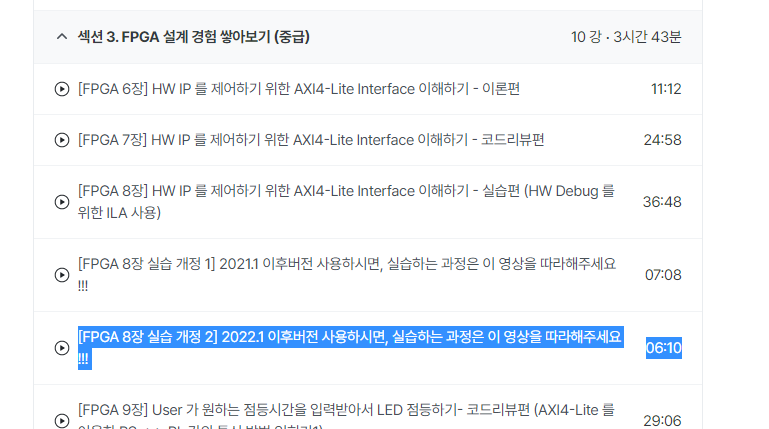

8장 오류 발생

1581

投稿した質問数 8

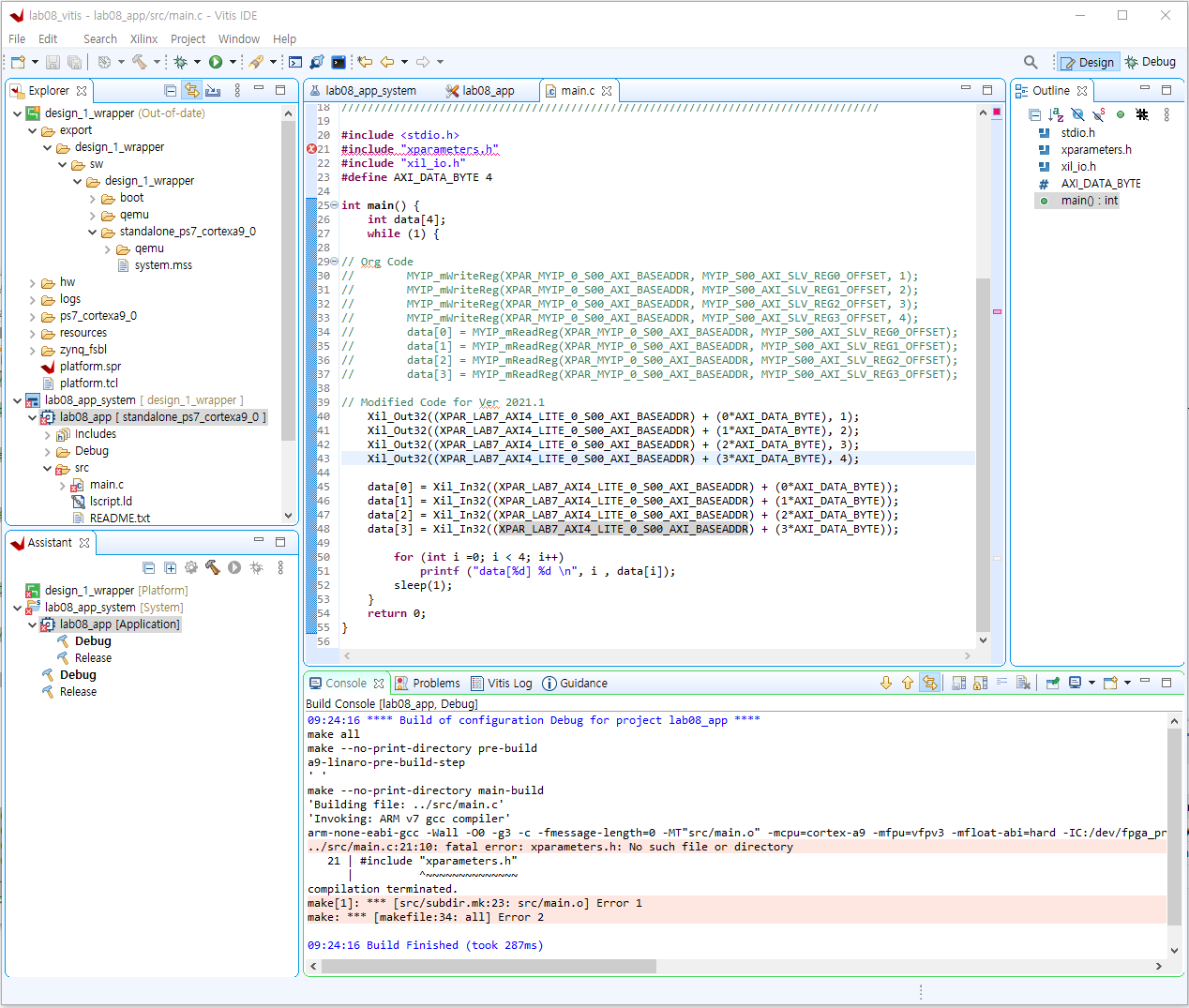

09:24:16 **** Build of configuration Debug for project lab08_app ****

make all

make --no-print-directory pre-build

a9-linaro-pre-build-step

' '

make --no-print-directory main-build

'Building file: ../src/main.c'

'Invoking: ARM v7 gcc compiler'

arm-none-eabi-gcc -Wall -O0 -g3 -c -fmessage-length=0 -MT"src/main.o" -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -IC:/dev/fpga_proj/lab08_vitis/design_1_wrapper/export/design_1_wrapper/sw/design_1_wrapper/standalone_ps7_cortexa9_0/bspinclude/include -MMD -MP -MF"src/main.d" -MT"src/main.o" -o "src/main.o" "../src/main.c"

../src/main.c:21:10: fatal error: xparameters.h: No such file or directory

21 | #include "xparameters.h"

| ^~~~~~~~~~~~~~~

compilation terminated.

make[1]: *** [src/subdir.mk:23: src/main.o] Error 1

make: *** [makefile:34: all] Error 2

09:24:16 Build Finished (took 287ms)

回答 2

1

(새로 촬영해서 업로드해주신 수업 내용 기반으로 해결방법 메모)

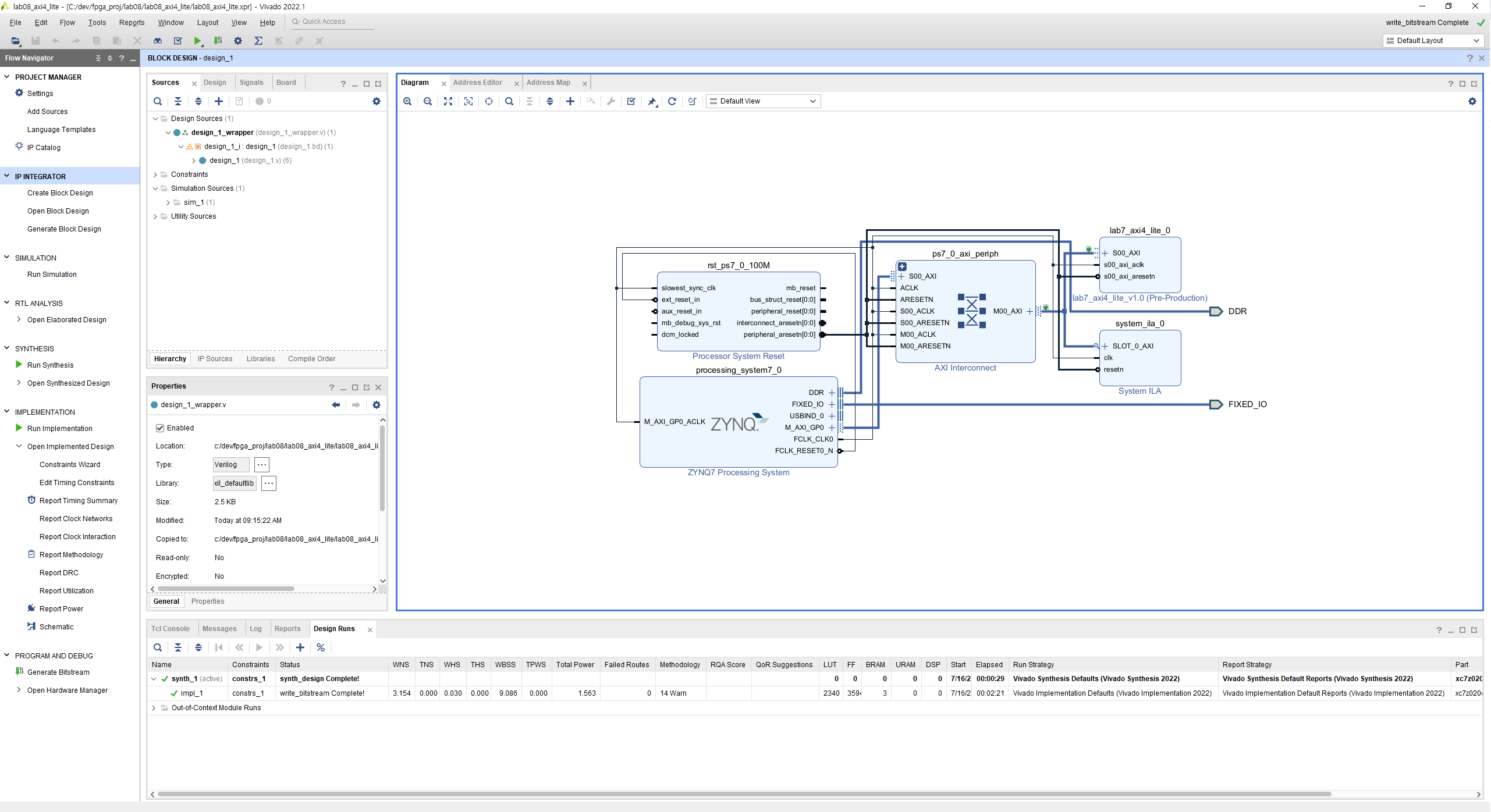

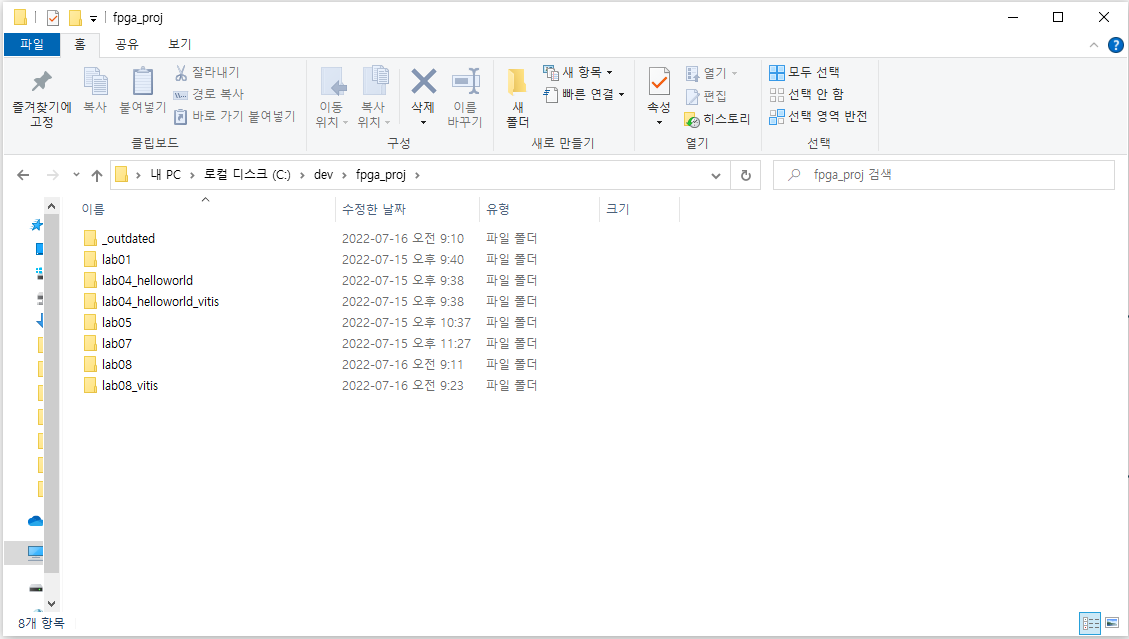

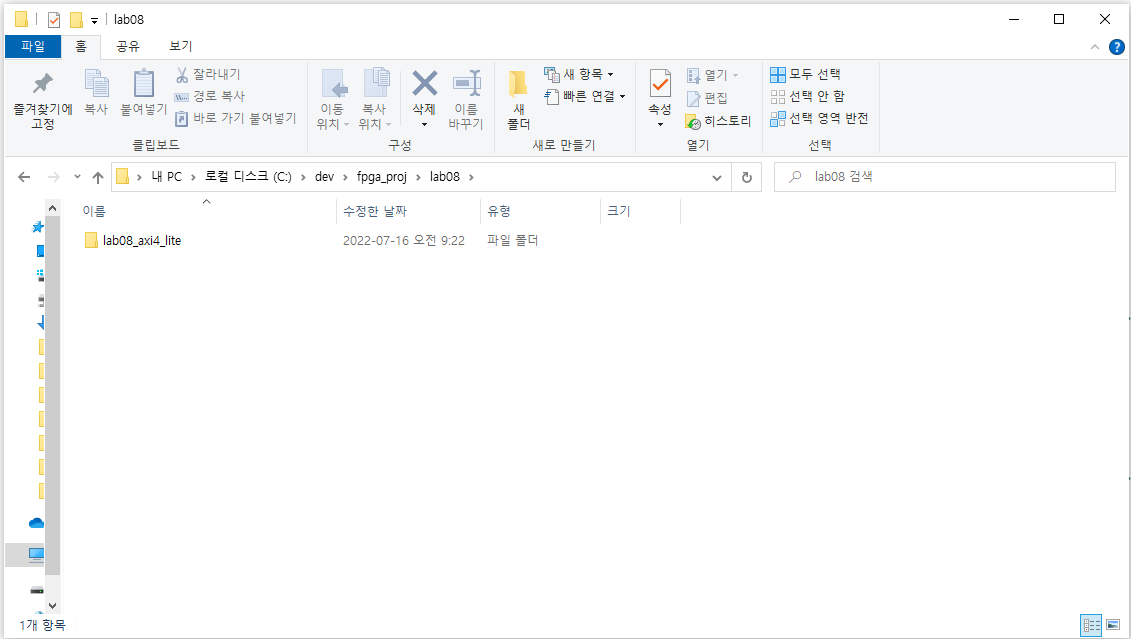

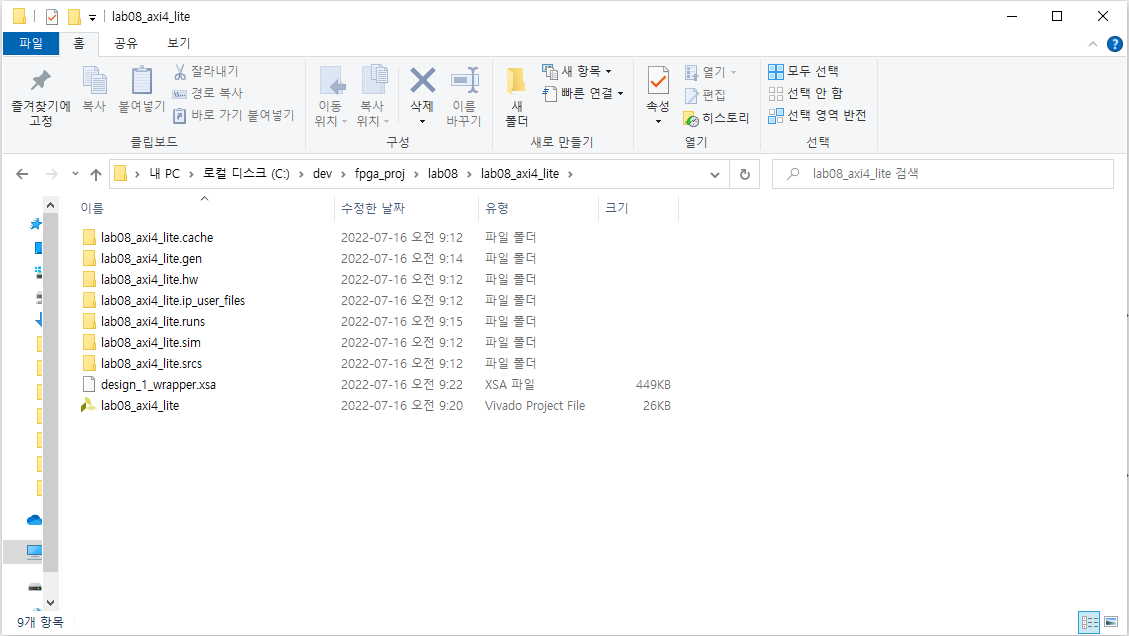

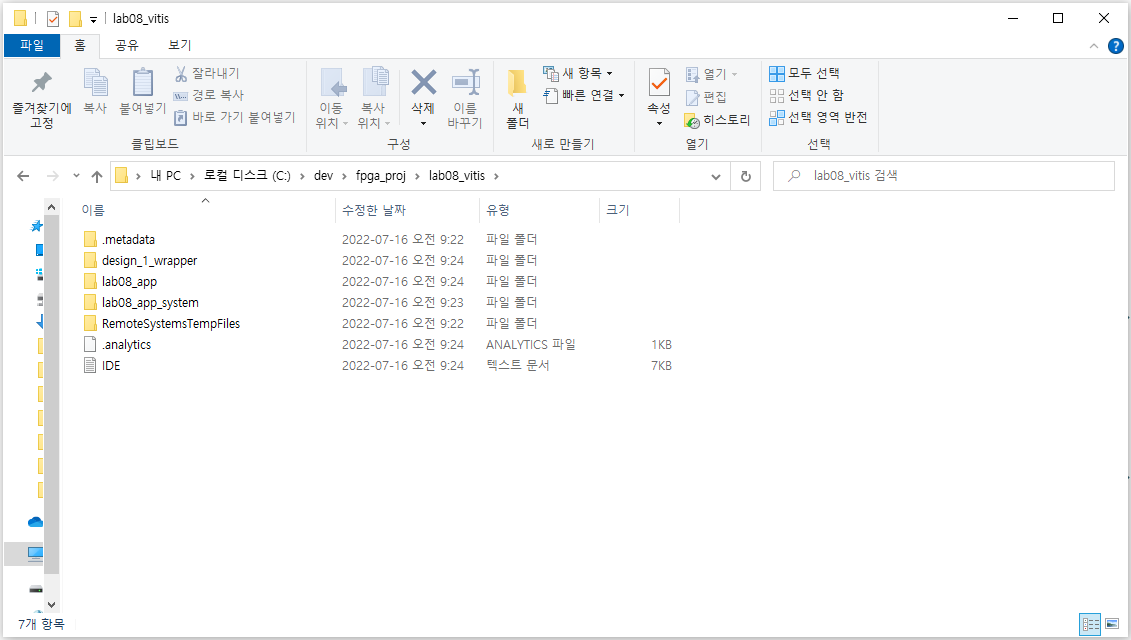

다음 두 경로(프로젝트 명에 따라 파일 이름이 다를 수 있음)에 들어가면 myip_v1_0 이라는 폴더가 있고, 그 폴더의 src 내부에 Makefile이 있음.

[1] design_1_wrapper>ps7_cortexa9_0>standalone_ps7_cortexa9_0>bsp>ps7_cortexa9_0>libsrc>

[2] design_1_wrapper>zync_fsbl>zync_fsbl_bsp>ps7_cortexa9_0>libsrc>

다른 libsrc에 있는 임의의 Makefile(영상에서는 gpiops_v3_9 폴더 사용)을 복사해서 myip_v1_0 의 Makefile과 Replace 해준다. (다른 거 -> 내꺼)

*[1]과 [2] 두개를 모두 바꾸어주어야함.

여기서 추가로 BASE_ADDR의 문제를 수정해야 하기 때문에,

이 부분은 새로 업로드된 2022.v1 의 main.c 파일을 사용.

<Makefile>

DRIVER_LIB_VERSION = 1.0

COMPILER=

ARCHIVER=

CP=cp

COMPILER_FLAGS=

EXTRA_COMPILER_FLAGS=

LIB=libxil.a

CC_FLAGS = $(COMPILER_FLAGS)

ECC_FLAGS = $(EXTRA_COMPILER_FLAGS)

RELEASEDIR=../../../lib/

INCLUDEDIR=../../../include/

INCLUDES=-I./. -I$(INCLUDEDIR)

SRCFILES:=$(wildcard *.c)

OBJECTS = $(addprefix $(RELEASEDIR), $(addsuffix .o, $(basename $(wildcard *.c))))

libs: $(OBJECTS)

DEPFILES := $(SRCFILES:%.c=$(RELEASEDIR)%.d)

include $(wildcard $(DEPFILES))

include $(wildcard ../../../../dep.mk)

$(RELEASEDIR)%.o: %.c

${COMPILER} $(CC_FLAGS) $(ECC_FLAGS) $(INCLUDES) $(DEPENDENCY_FLAGS) $< -o $@

.PHONY: include

include: $(addprefix $(INCLUDEDIR),$(wildcard *.h))

$(INCLUDEDIR)%.h: %.h

$(CP) $< $@

clean:

rm -rf ${OBJECTS}

rm -rf $(DEPFILES)

이상.

빌드 후 바이너리 생성파일 성공 확인 완료!

1

안녕하세요 :)

잘 따라하셨고요. 이해하기 좋게 상세히 적어주셔서 정말 감사드립니다.

저도 따라해보니 재현이 되었고, 2022.1 의 Tool 버그 로 판단을 하였습니다.

(게으른 Xilinx 가 여럿 사람들을 고생시키네요 ㅠ.ㅠ)

해결방법은 영상으로 별도로 올렸고요. 현재 인코딩 중이니, 고화질로 보실려면 내일 (220717) 오전에 확인해보시면 될 것 같아요.

즐공하셔요 :)

0

아하, 툴의 버전 문제였군요!

우와 ㅠ_ㅠ 이렇게 빠르게 답변해주시는 것을 넘어

새로운 버전의 문제로 인한 영상까지 이런 속도로 만들어주시다니

정말로 감사드리고, 감동입니다! 감사합니다!!

UART0, 1 중 선택

1

51

2

datamoverbram모듈질문

1

63

2

vitis 설치엣 alveo kria versal 등 옵션을 끄고 설치를 했습니다.

1

96

2

vitis 설치 관련 질문 있습니다!

1

84

2

FPGA 공식문서 읽는법

1

95

2

보드 추가의 클릭창이 없습니다.

1

71

2

Edit in IP Packager에서 코드 수정 후 IP 수정하면 simulation에서 수정된 코드로 작동이 안됩니다

1

81

2

BRAM의 Read / Write를 다 수행했는지 확인할 때 사용되는 num_cnt / i_num_cnt 관련 질문

1

106

1

Vitis 코드 작성

1

130

2

vivado 및 vitis 리눅스 환경 설치 관련 질문드립니다.

1

291

3

[9장 led 점등 시간 제어 불가]

1

81

2

Platform Invalid 오류

1

150

3

WSL 설치 관련 문의드립니다!!

1

96

2

Vivado 툴, 파일 질문드립니다!

1

151

2

9장 LED 점등 안됨

1

110

3

Edit in IP Packager 이후에

1

82

1

Fpga 로직

1

89

2

pmu-fw is not running

1

127

2

Create Project에 대해서 궁금해요

1

89

2

장치관리자 USB 포트

1

98

2

FPGA 7장 AXI_LITE I/F질문

1

89

1

bram mover에서 합성할때

1

77

2

타이밍 위반 질문

1

78

2

rvalid 초기화

1

66

2