안녕하세요.

얼마전에 중지되었던

전자문서 (pdf 파일) 다운로드가 다시 가능해졌습니다.

인프런에서 강의를 구매하신 분들은

자료실에서 전자문서를 다운로드해서 활용하시길 바랍니다.감사합니다~!!

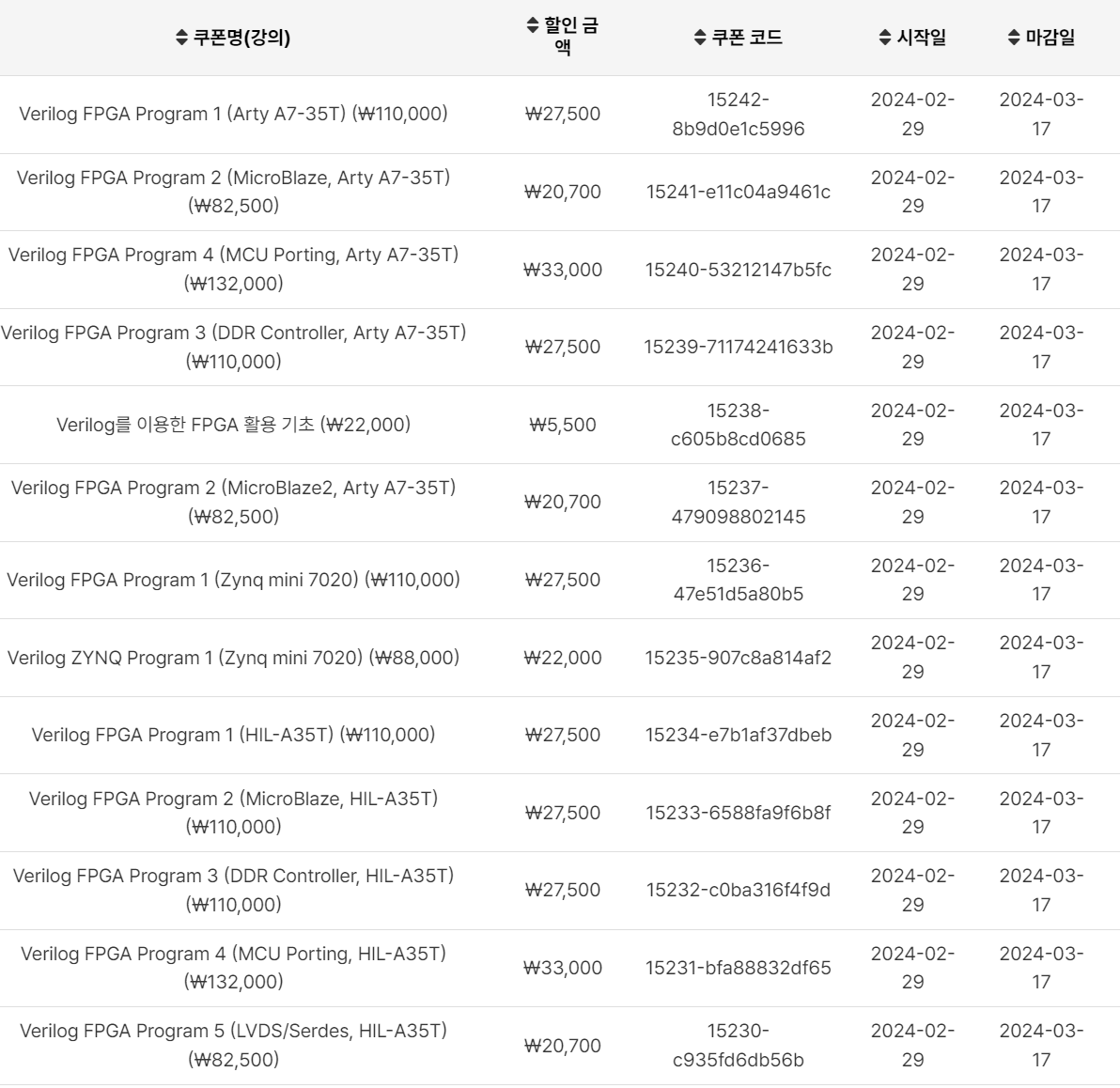

새학기를 맞이하여 강의 개별 구매 할인 이벤트를 진행합니다.

Verilog, FPGA를 배우고자 하시는 분들에게 좋은 기회가 되시길 바랍니다1. Verilog, FPGA 관련 강의 할인 이벤트

♣ 강의 25% 할인

♣ 기간 : 2024. 02. 29 ~ 2024. 03. 17

♣ 아래에 있는 할인쿠폰을 이용하여 인프런에서 구매2. HIL-A35 개발 보드 할인 이벤트

♣ 개발보드 15% 할인

♣ 기간 : 2024. 02. 29 ~ 2024. 03. 17

♣ 스마트스토어 : https://smartstore.naver.com/ihil감사합니다~!!

안녕하세요.

개발 보드 판매를 시작합니다.

아래 네이버 스마트스토어에서 구매하실 수 있습니다.

스마트스토어 링크 : https://smartstore.naver.com/ihil 개발보드 관련 자료는 아래 링크에서 다운로드할 수 있습니다.

개발보드 관련 자료는 아래 링크에서 다운로드할 수 있습니다.

매뉴얼과 테스트 프로그램(led, 버튼 동작)이 있습니다.

다운로드 링크 : http://naver.me/xJqtlt1TVerilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Controller, HIL-A35T)

Verilog FPGA Program 4 (MCU Proting, HIL-A35T)

개발보드와 강의 통해 많은 도움이 되시길 바랍니다.

감사합니다 ~!!안녕하세요.

강의용 개발보드가 10월 말경에

네이버 스마트스토어를 통해 출시 예정입니다.개발보드에 맞게 기존의 강의도 새롭게 만들어서 오픈예정입니다.

강의가 개발보드에 따라 다양하게 구성됩니다.

HIL-A35T (자사 개발 보드, 출시 예정)

Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Cotnroller, HIL-A35T)

Verilog FPGA Program 4 (MCU Porting, HIL-A35T)

Arty A7-35T (Digilent 개발 보드)

Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze2, HIL-A35T)

Verilog FPGA Program 3 (DDR Cotnroller, HIL-A35T)

Verilog FPGA Program 4 (MCU Porting, HIL-A35T)

Zynq mini 7020

Verilog FPGA Program 1 (Zynq mini 7020)

Verilog ZYNQ Program 1 (Zynq mini 7020)

Arty a7-35T, Zynq mini 7020 강의를 구매하신 분들에게는

HIL-A35T 강의를 초특가로 구매할 수 있도록 할 예정입니다.

그동안 개발보드로 인해 어려움이 있으신 분들에게

많은 도움이 될 수 있도록 노력하겠습니다.1차로 개발보드 수량은 50여개가 진행됩니다.

혹 필요하신 분들은 미리 연락주시면 감사하겠습니다.

가격은 18만원(부가세 별도) 정도 예상합니다.

(연락처 : alex@ihil.co.kr, 010-6243-0395)감사합니다~!!

강의가 업데이트 되었습니다.

강의명 : FPGA MicroBlaze 구현

업데이트 내용 : 4장, 5장 내용 새롭게 업데이트 됨.

강의를 구매하신 분은 자료실에서 다운받으시길 바랍니다.

추후 "FPGA MicroBlaze 구현" 강의는 계속해서 전체 내용이 업데이트 예정입니다.

감사합니다 ~!!

강의가 업데이트 되었습니다.

Verilog를 이용한 FPGA 활용 (v2.1)

NRZL Decoder 구현 내용(ch11)이 추가되었습니다.

FIFO 구현, 사용에 대한 중요한 내용입니다.

실무에 많은 도움이 될 것으로 기대합니다.

Verilog를 이용한 FPGA 활용 for Zynq (v1.2)

NRZL Decoder 구현 내용(ch14)이 추가되었습니다.

FIFO 구현, 사용에 대한 중요한 내용입니다.

실무에 많은 도움이 될 것으로 기대합니다.

강의를 구매하신 분들은 자료실에서 무료로 다운로드 받으시면 됩니다.

강의 통해 많은 도움 되시길 바랍니다.감사합니다.

안녕하세요.

[Verilog를 이용한 FPGA 활용 for Zynq] 강의가 오픈되었습니다.

본 강의는 [Verilog를 이용한 FPGA 활용]의 내용을 Zynq mini 7020(7010) 보드에 맞게

새롭게 구성하였습니다.전반부

vivado 2021.1 설치

Zynq 보드에 구현된 코드 다운로드 및 결과 확인

후반부

Counter를 이용한 LED 제어

SPI Controller

UART Controller

I2C Controller

Xilinx IP

강의 오픈 기념으로 30% 할인을 진행하고 있으니

많은 관심 부탁드립니다.감사합니다.

Verilog, FPGA 강의가 완료되었습니다.

처음에는 이정도까지 할거라 생각하지 못하였는데,

많은 분들이 도움주시고 호응해 주셔서

여기까지 올 수 있었던 것 같습니다.

제 강의에 관심 가져주신 모든 분들께 진심으로 감사드립니다.강의 활용팁에 대해서 간단히 설명드립니다.

1. 강의를 듣기 전에 Verilog 기본적인 문법을 숙지하시길 바랍니다.

강의에서 문법에 대해서는 설명하지 않습니다. 기본적인 문법을 알고 있는 것으로 생각하고 강의가 진행됩니다. 문법은 기본적인 것들만 알고 있으면 됩니다 (reg, wire, always, module, 등등)2. 처음 시작은 "Verilog를 이용한 FPGA 활용"부터 시작하시길 바랍니다.

이 강의안에 많은 내용들이 포함되어 있습니다.

2~3번 정도 정독하시면서 직접 코드로 구현하고 simulation으로 검증하고, 보드에 올려서 확인해 보시길 바랍니다.

verilog, fpga를 배우려면 눈으로 배우는 것은 아무 소용이 없습니다.

저는 총 개발경력이 25년에, verilog, fpga분야에서는 20년 정도 되었습니다.

지금도 i2c contoller 구현하려면 수십번 넘게 코딩하고 simulation 검증하고 이러한 과정을 거치게 됩니다.

강의 소개 : https://cafe.naver.com/worshippt/2663. "Verilog를 이용한 FPGA 활용 기초" 편은 부록으로 활용하시길 바랍니다.

한번쯤은 아셔야 할 내용들로 구성되었습니다.

본 강의는 추후 내용을 추가하여 업데이트할 예정입니다.

강의 소개 : https://cafe.naver.com/worshippt/2654. FPGA MCU 포팅 강의는 개발자의 스킬을 한단계 업그레이드 할 수 있는 내용입니다.

저는 수많은 프로젝트에 본 강의의 내용을 적용하였습니다.

로직을 디버깅하는 용도로도 사용되고, 별도의 MCU를 외부에 사용할 필요가 없는 매우 유용한 solution입니다.

뿐만 아니라, 자유롭게 fpga 내부의 Memory 들을 활용할 수 있습니다.

강의 소개 : https://cafe.naver.com/worshippt/2685. MicroBlaze 강의는 2편의 강의 내용을 제대로 이해 한다면 거의 모든 내용을 알고 프로젝트에 적용할 수 있습니다.

MicroBlaze는 MCU 포팅에 비해서 성능이 매우 좋습니다.

반면에 메모리를 구성하고 적용하는 부분에 약간의 제약들이 있습니다.

MCU 포팅, MicroBlaze 2개를 모두 알고 있으면 프로젝트에 따라서 선택하여 사용할 수 있습니다.

가볍게 사용하고 싶을 때에는 MCU 포팅을 사용하고, 성능이 좋은 것이 필요하면 MicroBlaze를 사용하면 됩니다.

강의 소개-1 : https://cafe.naver.com/worshippt/269

강의 소개-2 : https://cafe.naver.com/worshippt/2706. DDR Controller 강의는 Image Data를 처리하는 분야에 필요한 강의입니다.

Image Data를 처리하기 위해서는 Frame Buffer가 필요하고, Frame Buffer는 대부분 DDR Memory를 사용합니다.

본 강의는 DDR Controller 생성부터 Framer Buffer를 구현하는 내용까지 설명되어 있습니다.

강의 소개 : https://cafe.naver.com/worshippt/267향후에는 더 좋은 내용으로 찾아뵐 수 있도록 하겠습니다.

저의 강의에 관심 가져 주신 분들께 다시한번 감사드립니다.감사합니다.