-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

22강 FC에서 BRAM을 추가해보려 하였습니다.

24.05.02 17:15 작성 24.05.02 18:28 수정 조회수 113

1

안녕하세요.

22장 수강 후, HW 가속기를 직접 설계 해보는 너무나 좋은 경험을 하였습니다.

1) 첫번째 질문

강의를 직접 수강 후, 보통의 DNN에서는 Wieght만 있는 것이 아닌 Bias또한 존재하기 때문에 기존에 사용하던 BRAM을 2개에서 3개로 (Bias 값을 담는 BRAM 추가) 하여 다시 설계해보았습니다.

https://sturdy-nebula-796.notion.site/AI-H-W-Spec-2ffdd93b8dec4e9d92660514d7b63df4?pvs=25

( 연산 FC Core에 Relu 와 Bias를 추가하였습니다.)

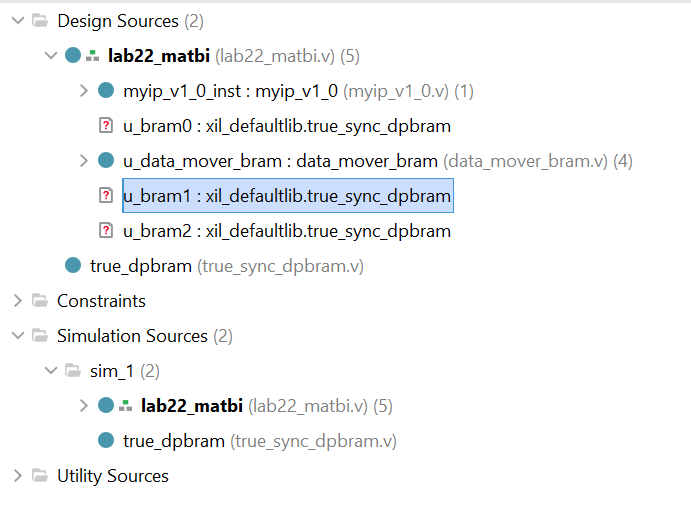

그 후 Vivado에서 합성한 결과 아래 사진 처럼 BRAM이 합성되지 않은것을 확인하였습니다.

코드를 여러번 보면서 어디서 문제가 된건지 확인했지만, 찾을 수 없었습니다.

맛비님께서 바쁘시니 감으로라도 이런 부분에서 문제가 있을것 같다 하시면 제가 찾아서 한번 수정을 여러번 진행해보겠습니다.. ㅜㅜ

2) 두번째 질문

보통 DNN의 FC Layer의 hidden Layer과 Output Node의 갯수는 256~512개 정도로 설정하여 학습하는것으로 알고있습니다. (CNN이 아님)

강의에서는 Output Node를 4개로 설정하였고, 그에 4개의 Output Register를 설정하였습니다.

만약, 그렇다면 Output Node나 Hidden layer Node를 n ( n>200) 이라고 한다면, Output 값을 받아줄 Register 갯수와 연산할 Core의 갯수도 n개로 맞춰줘야 하는지 궁금합니다.. (무언가 다른 방법이 있는지도 궁금합니다.)

좋은 강의해주셔서 정말 감사합니다. 맛비님

답변을 작성해보세요.

1

0

설계독학맛비

지식공유자2024.05.03

안녕하세요 🙂

실수 할 수 있죠!! 죄송해 하지 않아도 됩니다 🙂

만약, 그렇다면 Output Node나 Hidden layer Node를 n ( n>200) 이라고 한다면, Output 값을 받아줄 Register 갯수와 연산할 Core의 갯수도 n개로 맞춰줘야 하는지 궁금합니다.. (무언가 다른 방법이 있는지도 궁금합니다.)

core 수를 늘리면 Area 가 늘어나는 trade off 관계를 이해하면 될 것 같아요.

결국 n 이 200개이던 2000개이던, 그 이상이던, Core 를 재사용하는 방식을 사용하면 됩니다. 실제 많은 GPU, NPU 들이 이런 방식을 사용합니다.

연산기는 MAC 인데, input node 의 값과 weight 만 적절히 바꿔줄 수 있다면 가능하겠죠.

200 개를 한번에 200개의 core 를 계산하느냐, 4개의 core 로 50번을 나눠서 계산하느냐의 문제 같아요.

즐공하세요 🙂

0

인프런 AI 인턴

2024.05.02

안녕하세요, 인프런 AI 인턴입니다.

주노님의 질문에 대해, 관련 질문 및 지식공유자 설계독학맛비님의 답변을 찾아보았습니다. 본 답변이 주노님의 궁금증을 해결하는 데 도움이 되길 바랍니다.

- BRAM 추가 관련 질문

직접 BRAM을 추가하신 경험은 매우 좋은 도전입니다. BRAM 추가 시 발생할 수 있는 문제는 여러 원인에서 기인할 수 있으므로, 맛비님의 답변 중 관련 내용을 찾아보았습니다.

BRAM과 관련하여, FPGA 22장 전체 HW 연산 시간 관련 질문에서 더블 버퍼링(double buffering) 기법과 병렬 실행 가능성에 대한 해답을 찾으실 수 있습니다. 해당 답변에서 맛비님은 BRAM의 데이터 전송 과정에서 병렬 처리가 가능함을 설명하셨습니다. 이는 BRAM 추가 및 구성 시 문제 해결의 단서가 될 수 있습니다.

- DNN FC Layer 구성 관련 질문

Output Node나 Hidden layer Node 수의 증가에 따른 처리 방식에 대해 lab22_main.c 관련 문의에서 맛비님은 double buffering 방식을 제안하셨습니다. 여기서는 데이터 병렬 처리 방식에 대한 방향성을 제시했습니다. 비록 직접적으로 Output Node 증가에 따른 Register 갯수 적용에 대한 내용은 아니지만, 맛비님의 설명에서 HW 가속기 설계의 이해를 돕는 내용을 얻으실 수 있을 것입니다.

또한, 맛비님께서는 HW 가속기 설계에서 데이터 로딩 속도가 성능에 큰 영향을 미칠 수 있음을 강조하셨습니다. 설계 과정에서 고려해야 할 중요한 점으로, 실험을 통해 최적의 설계 방법을 찾을 필요가 있습니다.

BRAM 추가 및 DNN FC Layer 구성에 대한 질문은 FPGA 설계와 관련된 고급 주제로, 구체적인 답변을 얻기 위해서는 다양한 시도와 실험이 수반되어야 합니다. 맛비님의 기존 답변들을 참조하여 문제 해결의 단서를 찾아보시고, 추가적인 실험을 통해 원하는 결과를 얻기 바랍니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

답변 3