월 77,000원

5개월 할부 시

중급자를 위해 준비한

[반도체, 임베디드 · IoT] 강의입니다.

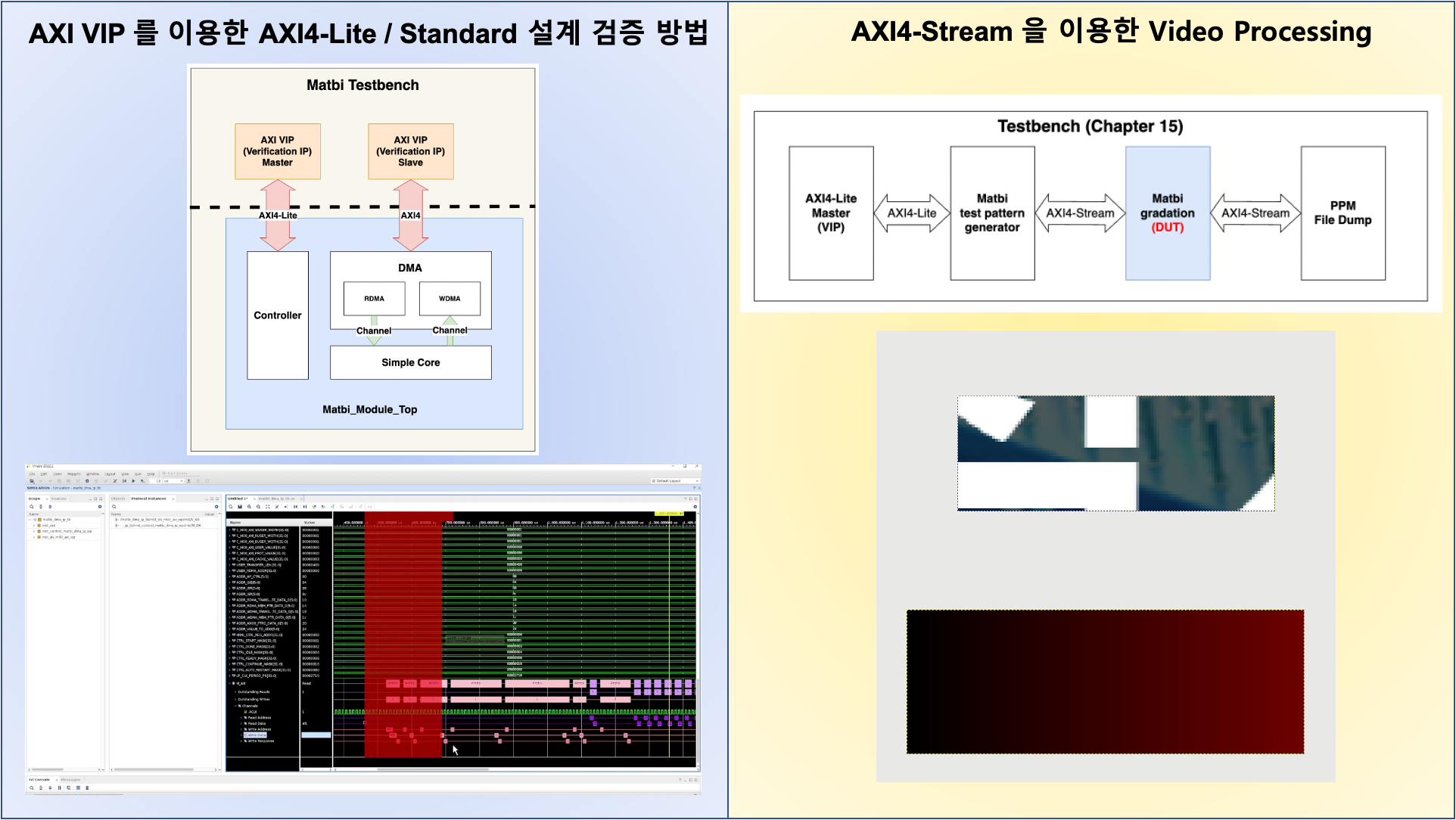

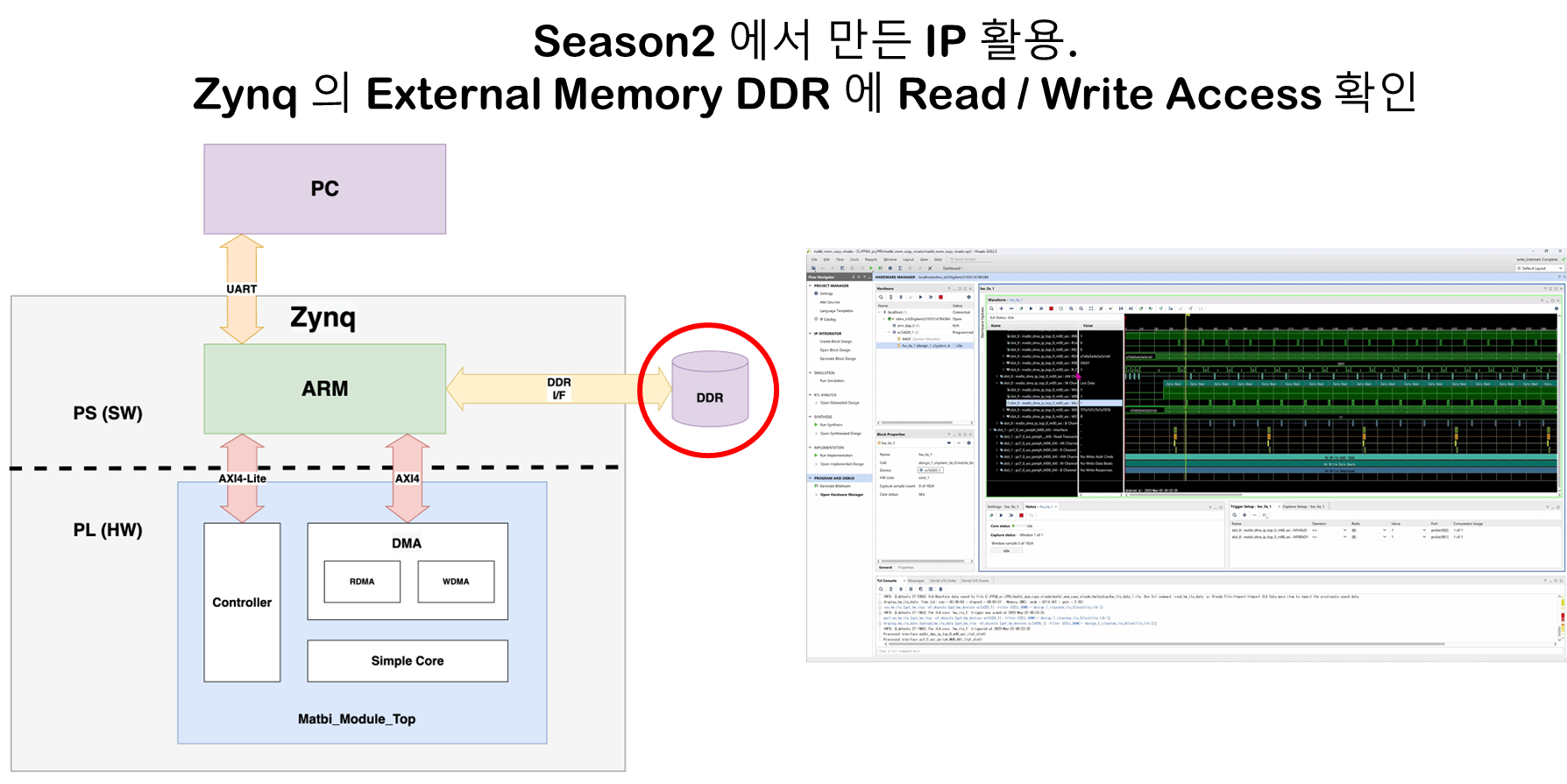

설계독학과 함께 Verilog HDL을 이용하여 SoC Bus의 기본이 되는 AMBA AXI4 설계와 VIP 검증 경험을 쌓아봅시다!

이런 걸

배워요!

비메모리 설계 엔지니어가 알려주는

실전 Verilog HDL: AMBA AXI4 완전 정복!

비메모리 설계의 프로라면

반드시 알아야 할 AMBA

안녕하세요! 설계독학의 맛비입니다.

시즌 1에서 이어지는 이 강의에서는 설계/검증/시스템 아키텍터가 필수로 알아야 하는 AMBA(Advanced Microcontroller Bus Architecture)를 다룹니다.

✅

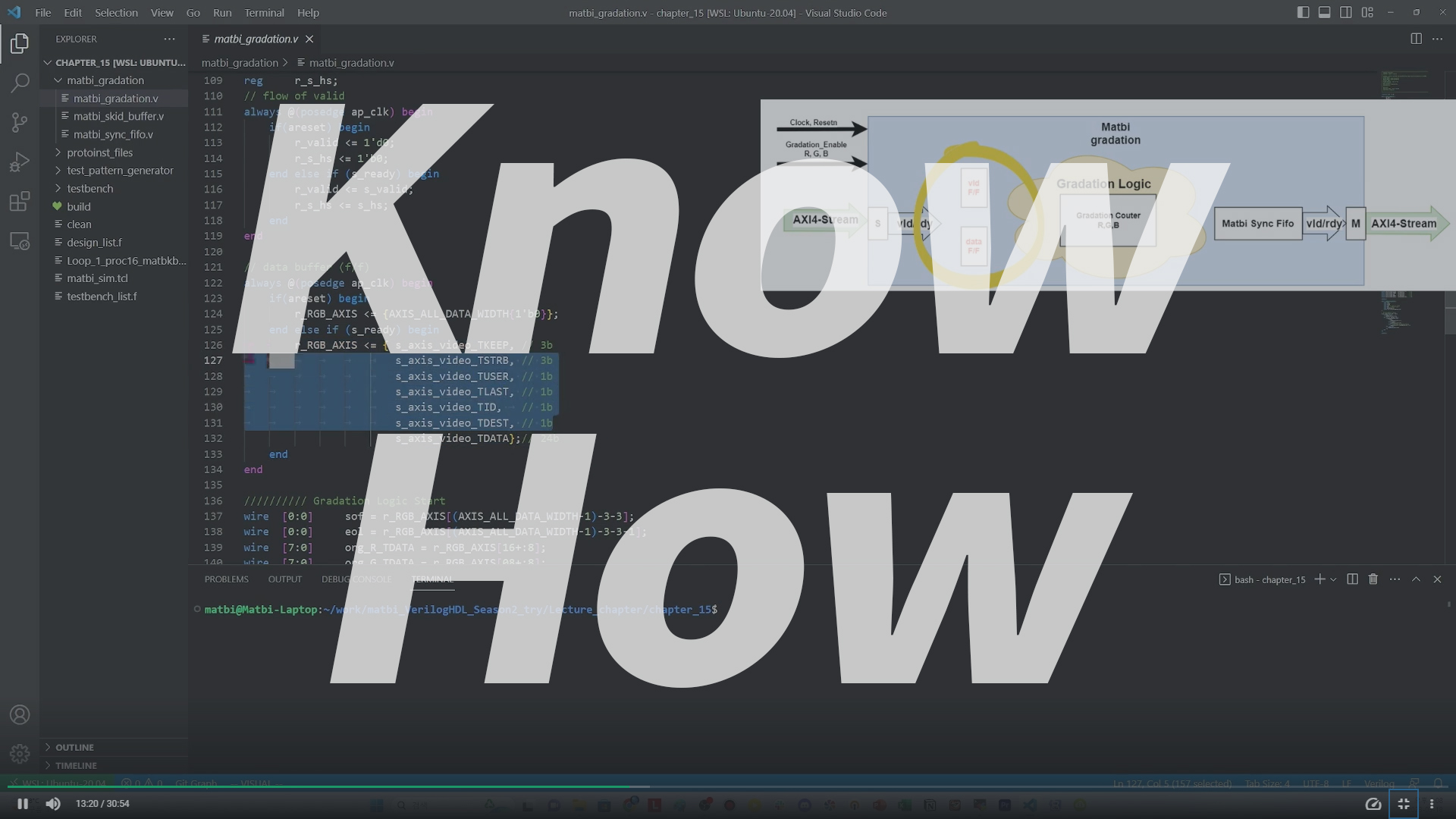

제가 현업에서 AMBA 관련 설계를 하면서 직접 경험한 노하우를 담았습니다.

✅

수강생 여러분들께 전해드릴 실습 코드만 1만 라인이 넘습니다.

✅

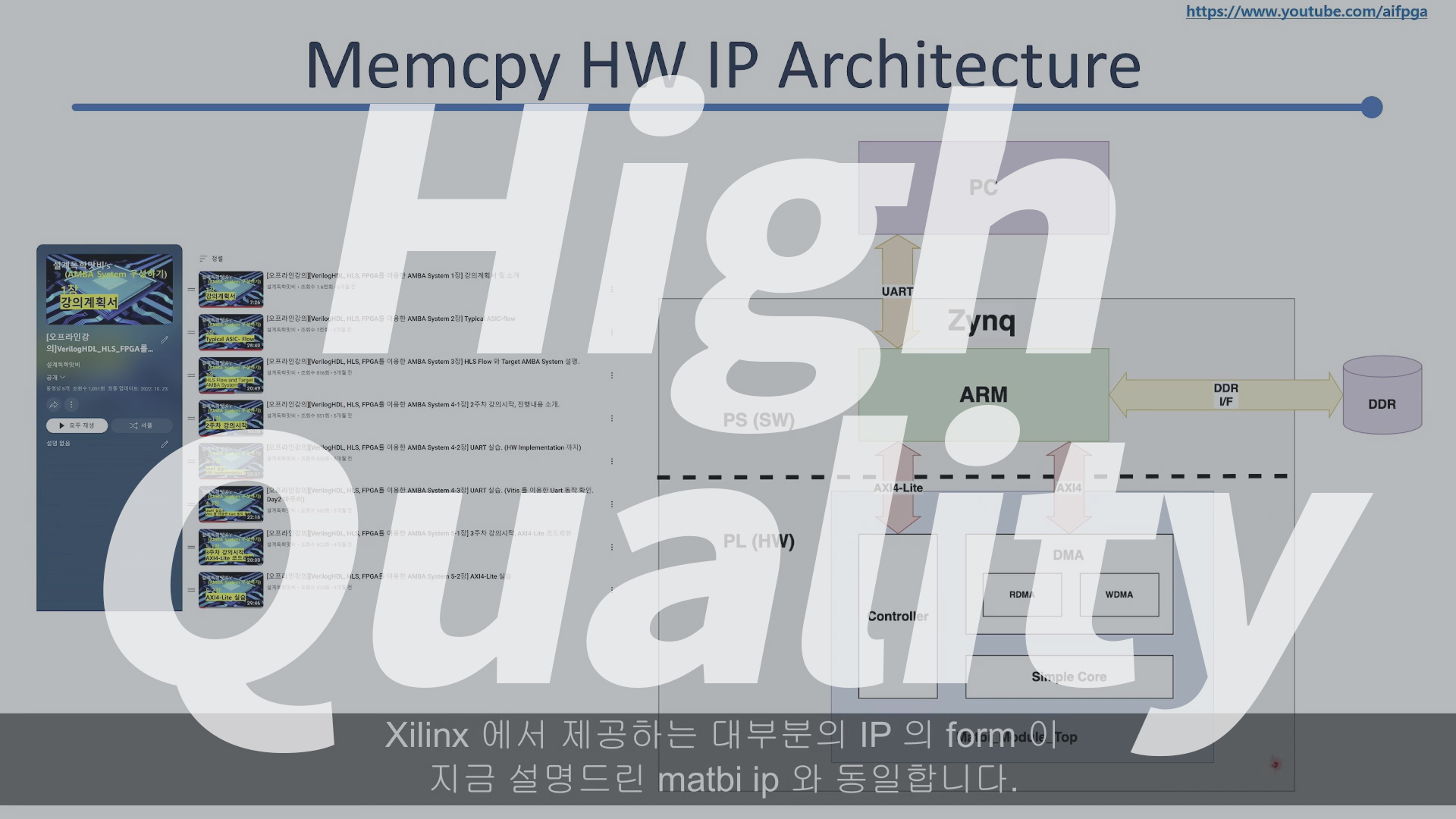

그 어떤 누구도 흉내낼 수 없는 설계독학만의 강의 퀄리티를 약속드립니다.

초보자 강의가 아닙니다!

비메모리 설계 경력 4~8년차 지식 수준을 목표로 하는 강의입니다.

이런 분들이 수강하시기를 적극 추천드립니다.

- 1️⃣ 설계에 흥미가 있고, 잘하고 싶다는 의지가 있으신 분 (가장 중요)

- 2️⃣ 반도체 분야 석, 박사 재학생

- 3️⃣ AMBA에 대해 경험하고 싶은 설계 현업자

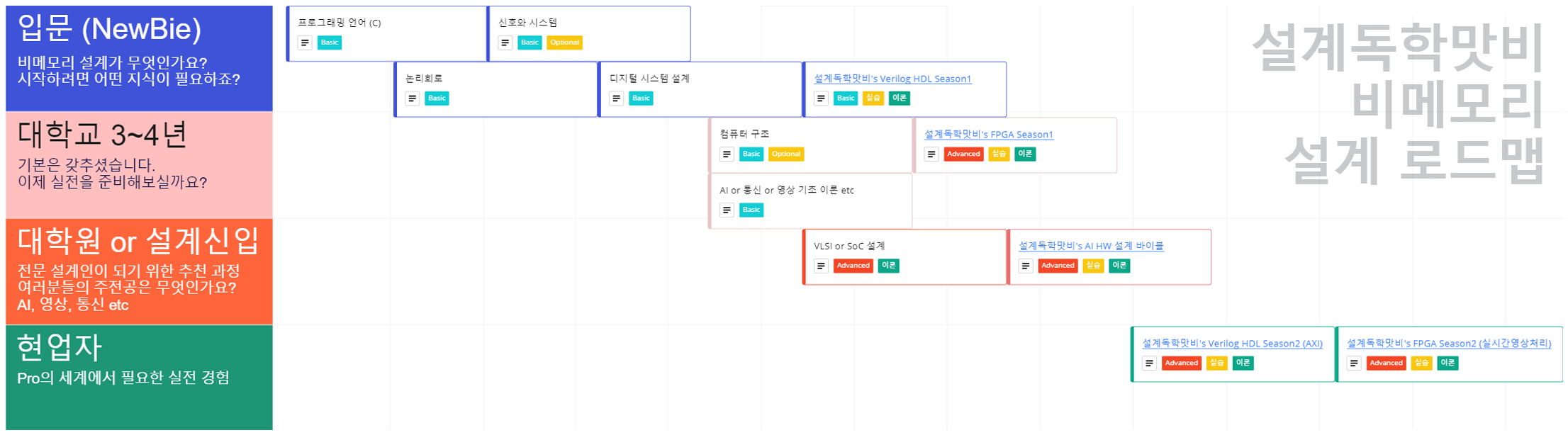

비메모리 설계 전문가를 꿈꾼다면? 설계독학맛비 로드맵

수강한다면, 비메모리 설계의

제대로 된 실력을 갖추게 됩니다.

- 비메모리 설계 엔지니어가 갖춰야 하는 기본 지식과 설계의 자신감을 얻을 수 있습니다.

- 찐 실무에서 필요로하는 필수 지식을 배울 수 있습니다.

- 마스터하신다면 4~8년차 엔지니어 이상의 설계 지식을 갖출 수 있습니다.

- 여러분들만의 HW IP를 설계하고 검증할 수 있습니다.

- 앞으로 이어질 설계독학맛비의 다양한 프로젝트 강의에서 이 지식을 적극 활용합니다.

설계독학의 강의가 차별화된 이유 📌

어설프게 배우지 마세요!

현업자의 노하우를 그대로 전합니다.

저는 설계를 하는 현업자입니다. 모든 내용을 직접 설계해본 다음 강의를 만들었습니다. 아는 척하는 어설픈 지식만 다루는 강의와는 다릅니다.

어설프게 배우지 마세요. 진짜 설계 엔지니어링 실무에 필요한 지식을 확실하게 전해드립니다.

여러분의 1분 1초가 소중하니까,

모든 수업을 설계독학이 직접 편집합니다.

동영상 러닝 타임이 다른 강의에 비해 짧게 느껴지시나요? 툴 러닝타임, 설명 도중 쉬는 시간, 어설픈 농담 등 쓸데없는 시간은 강의에 담지 않습니다.

제가 제공하는 이론과 실습 코드 전체를 익히는 데 타 강의에 비해 훨씬 알찬 호흡으로 학습할 수 있습니다.

공부할 모든 내용을

충분히 실습할 수 있도록.

현직자가 직접 설계한 고퀄리티 Verilog HDL 실습 코드

- AXI4-Lite / AXI4-Stream / AXI4-Standard

- 맛비가 직접 만든 이론 및 실습을 전부 다룹니다.

- FPGA 합성 가능합니다.

현업에서만 사용할 수 있는 AXI VIP 환경

- 강력한 AXI VIP 환경을 직접 경험해보세요.

- 검증된 무료 시뮬레이션 툴 Vivado Xsim을 사용합니다.

- FPGA에 올려 동작까지 확인했습니다.

- 사용했던 프로젝트 파일도 제공합니다.

한국에서 비메모리 설계 엔지니어가 된다면 💪

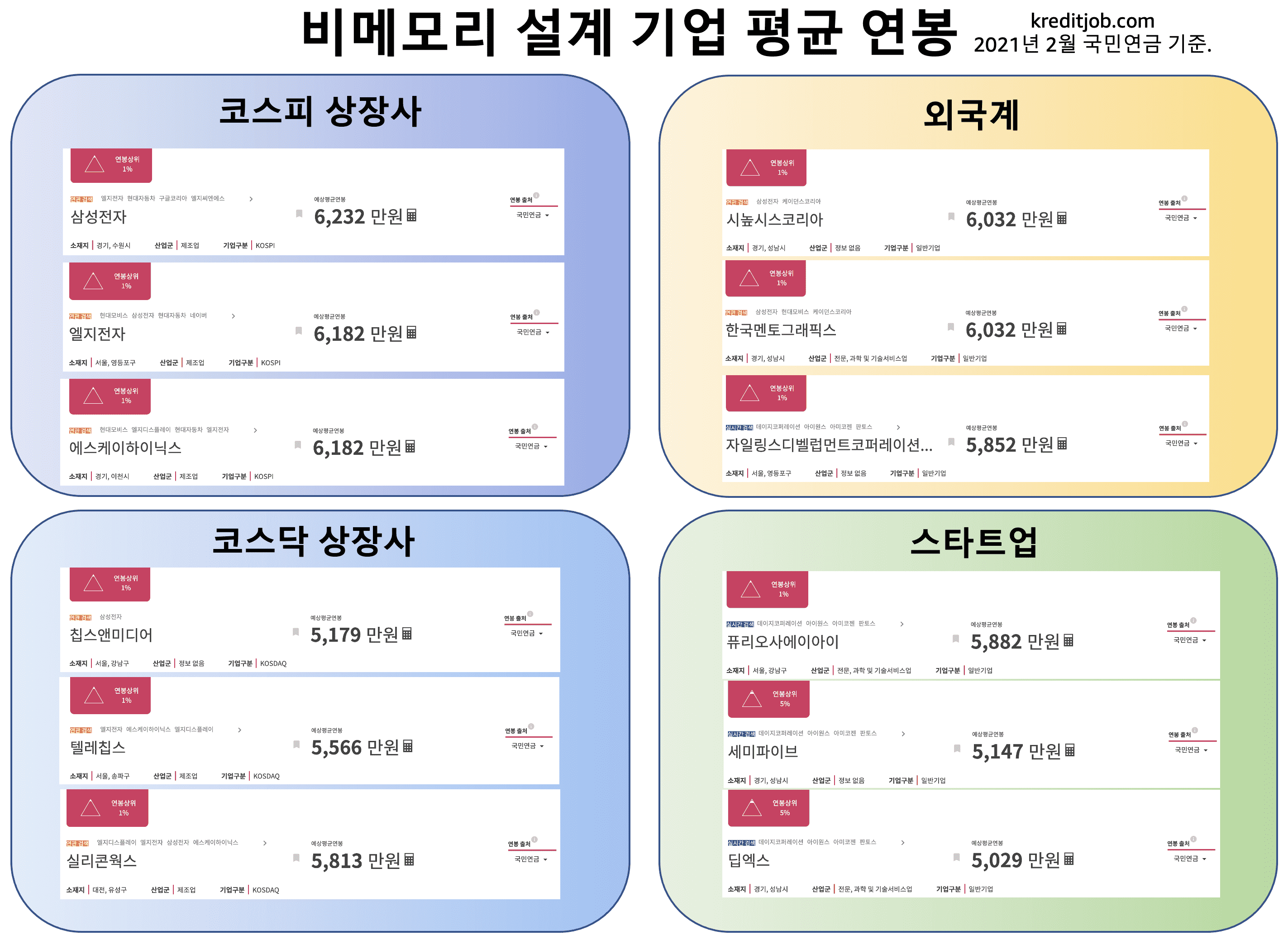

한국은 메모리 반도체 강국입니다. 비메모리 반도체 강국이 아닙니다. 때문에 정부와 기업이 많은 투자를 하고, 설계 회사도 여럿 있습니다. 취업 사이트에서 "Verilog HDL" 키워드를 검색해보세요. 전세계 많은 회사들이 반도체 설계 엔지니어를 찾고 있습니다. 가고 싶은 회사가 있으신가요? 그 회사의 연봉을 검색해보세요.

비메모리 설계 관련 회사들은 국내 기업 평균 연봉 상위 1%에 해당합니다. 받는 만큼 공부해야 하는 직업이고 쉬운 길이 아니지만, 그만큼 탄탄한 전망이 기다리는 일입니다.

현업에서 만나요 🖐

여기까지 읽어주셔서 진심으로 감사합니다.

여러분들은 훌륭한 설계 엔지니어가 되실 거라 확신합니다.

선택은 여러분들의 몫입니다.

여러분들을 현업에서 만나뵙기를 기대합니다.

감사합니다. 맛비 드림.

연관 강의가 궁금하다면?

🎁 학생, 취준생 분들께 할인 쿠폰을 드립니다! 🥰

아직 수입이 없는 분들의 부담을 조금이나마 덜어드리기 위해 마련했어요.

더 많은 분들에게 혜택이 돌아갈 수 있도록 양해 부탁드립니다. (신청 링크)

이런 분들께 추천드려요!

학습 대상은

누구일까요?

선수 지식,

필요할까요?

설계독학맛비 입니다.

안녕하세요. 설계독학의 맛비입니다.

현) Global Top10 Fabless 기업에서 HW IP 설계하고 있습니다.

반도체 설계관련 이야기들을 주제로 영상과 글을 쓰고 있습니다.

설계독학 유튜브, 설계독학 블로그, 맛비 블로그 (네이버)