-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

해결됨

실습응용편 질문입니다

21.04.27 20:04 작성 조회수 222

1

====== 질문 ======

질문이 좋았는데, 사라져서 대신 남깁니다. :)

1. Resistering count 부분을 꼭 작성해야 하나요?

Resistering count가 없어도 Core 에서 i_num_cnt에 따라서 카운트 되도록 표현 가능하지 않나요?

2. 카운트 변수를 초기화 시킬때 reset_n 으로 하는게 정석 같지만 i_run 신호로 해도 괜찮은건가요?

설계독학맛비's 실전 Verilog HDL Season 1 (Clock부터 Internal Memory까지)

[HDL 17장] HW 의 동작을 제어하는 FSM 을 이해해보자. (실습응용편)

강의실 바로가기

답변을 작성해보세요.

0

설계독학맛비

지식공유자2021.04.27

====== 답변 ======

안녕하세요 :)

1. Resistering count 부분을 꼭 작성해야 하나요?

Resistering count가 없어도 Core 에서 i_num_cnt에 따라서 카운트 되도록 표현 가능하지 않나요?

설계에 정답은 없습니다. 변경하시고 싶은대로 해보시고 만들면 돼요.

외부 입력으로 i_num_cnt 를 register count 를 대신한다면 없어도 됩니다.

하지만 누군가는 counting 을 해야 하고, 그 누군가의 위치를 저는 FSM couter 모듈안에 배치했어요.

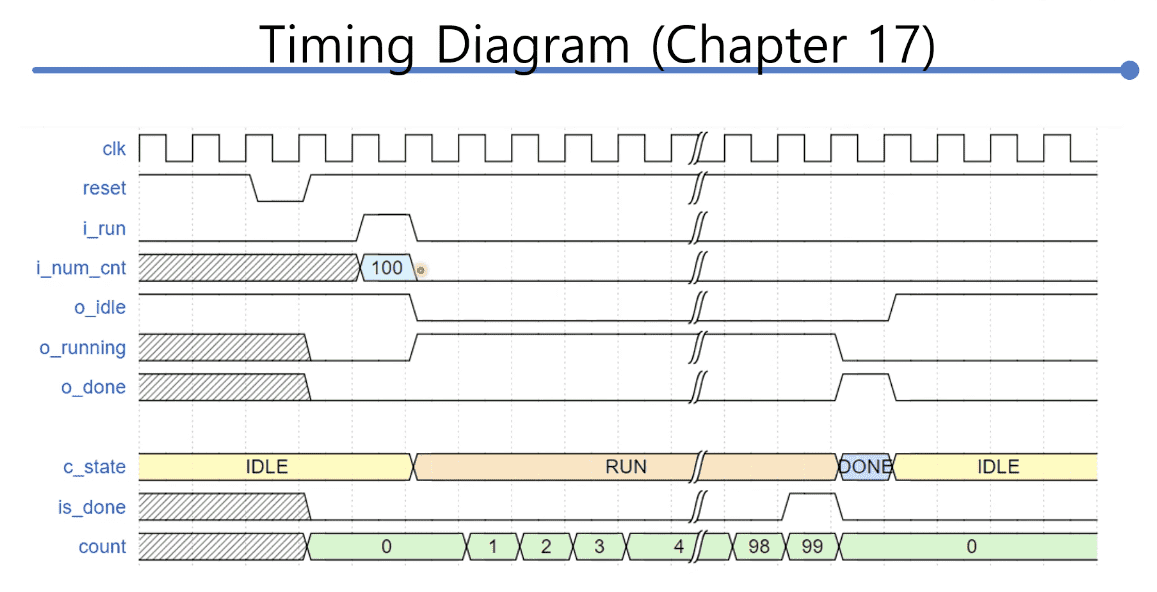

(꼭 작성해야 하냐? 는 다음 Timing diagram 을 spec 이라고 했을때 필요할 것 같습니다. 모듈 내부에서 counting 을 해야, 지금 spec 을 맞출 수 있겠죠.)

2. 카운트 변수를 초기화 시킬때 reset_n 으로 하는게 정석 같지만 i_run 신호로 해도 괜찮은건가요?

i_num 신호를 어떻게 사용하실지는 제가 이해를 못했습니다..만!

하지만 reset_n 신호 대신, 다른 signal 로 초기화는 가능합니다. (당연히 문법적으로 문제 없어요)

하지만 사용하려는 signal 로 Reset 을 해도 된다라는 Designer (설계자) 의 보장이 반드시 있어야 합니다.

결론은 가능하다.

그럼 즐공하세요 :)

답변 1