Verilog FPGA Program 4 (MCU Porting, Arty A7-35T)

How to port and use free MCU IP into an FPGA.

News

15 articles

hello.

It was stopped a while ago

Downloading electronic documents (pdf files) is now possible again.

Those who purchased the course from Infraon

Please download and use electronic documents from the data room.Thank you~!!

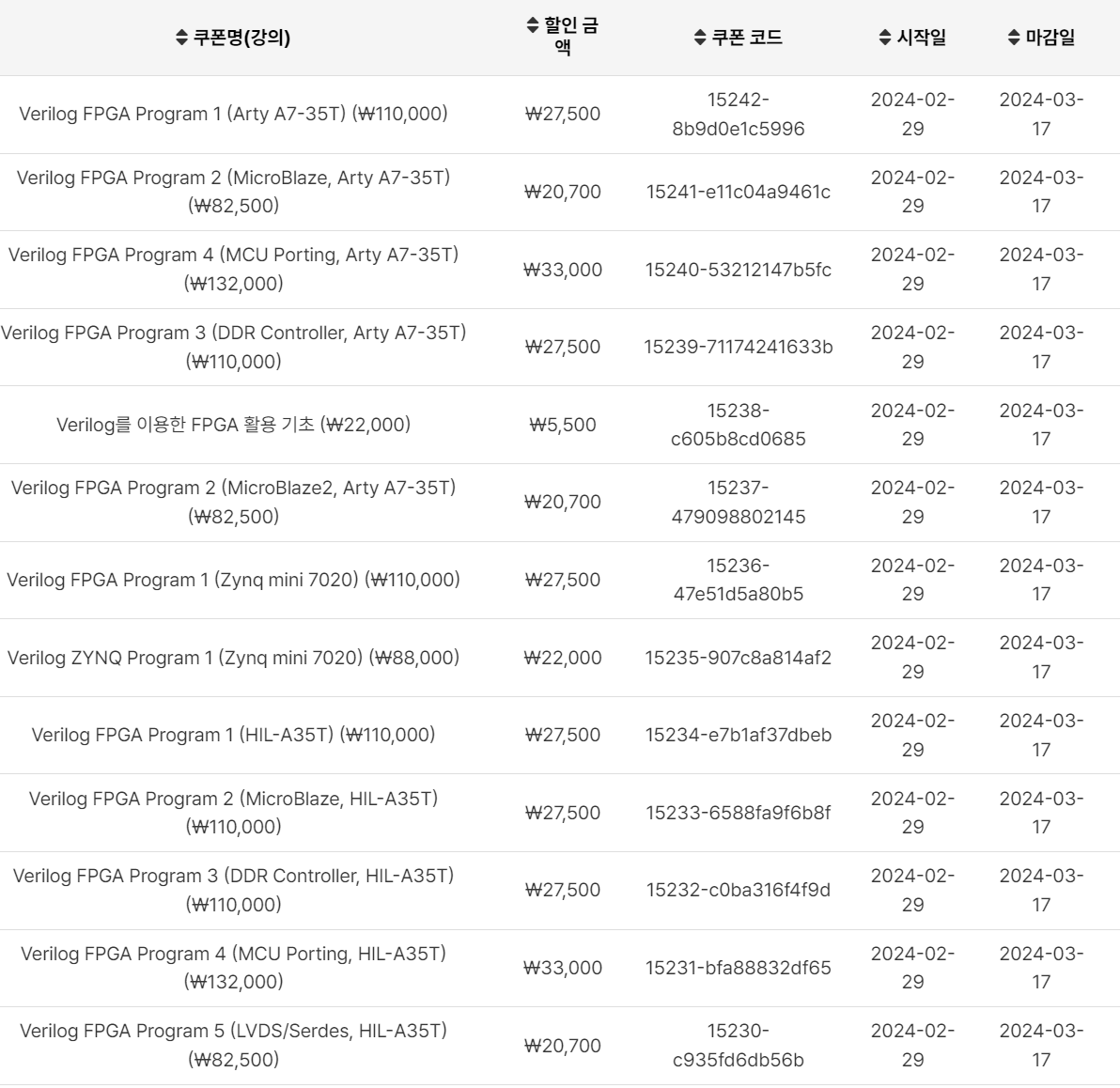

To celebrate the new semester, we are holding a discount event for individual course purchases.

I hope this will be a good opportunity for those who want to learn Verilog and FPGA.1. Discount event for lectures related to Verilog and FPGA

♣ 25% discount on lectures

♣ Period: 2024. 02. 29 ~ 2024. 03. 17

♣ Purchase from Infleun using the discount coupon below2. HIL-A35 Development Board Discount Event

♣ 15% discount on development boards

♣ Period: 2024. 02. 29 ~ 2024. 03. 17

♣ Smart Store: https://smartstore.naver.com/ihilThank you~!!

Hello.

We are starting to sell development boards.

You can purchase it from the Naver Smart Store below.

Smart Store Link: https://smartstore.naver.com/ihil Development board related materials can be downloaded from the link below.

Development board related materials can be downloaded from the link below.

There is a manual and a test program (led, button operation).

Download link: http://naver.me/xJqtlt1T The development board is a product developed in-house for use in Inflearn lectures.

The development board is a product developed in-house for use in Inflearn lectures.Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Controller, HIL-A35T)

Verilog FPGA Program 4 (MCU Proting, HIL-A35T )

I hope that the development board and lectures will be of great help to you.

Thank you~!!hello.

The development board for the lecture will be available around the end of October.

It is scheduled to be released through Naver Smart Store.We plan to re-create existing lectures to fit the development board and open them.

The lectures are structured differently depending on the development board.

HIL-A35T (our own development board, to be released)

Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Cotnroller, HIL-A35T)

Verilog FPGA Program 4 (MCU Porting, HIL-A35T)

Arty A7-35T (Digilent development board)

Verilog FPGA Program 1 (Arty A7-35T)

Verilog FPGA Program 2 (MicroBlaze, Arty A7-35T)

Verilog FPGA Program 2 (MicroBlaze2, Arty A7-35T)

Verilog FPGA Program 3 (DDR Cotnroller, Arty A7-35T)

Verilog FPGA Program 4 (MCU Porting, Arty A7-35T)

Zynq mini 7020

Verilog FPGA Program 1 (Zynq mini 7020)

Verilog ZYNQ Program 1 (Zynq mini 7020)

For those who purchased the Arty a7-35T, Zynq mini 7020 course,

We plan to make the HIL-A35T course available for purchase at a special price.

For those who have had difficulties with the development board,

I will try my best to be of help.The first round of development boards will be approximately 50 units.

If you need it, please contact us in advance. Thank you.

The price is expected to be around 180,000 won (excluding VAT).

(Contact: alex@ihil.co.kr , 010-6243-0395)Thank you~!!

The lecture has been updated.

Lecture Name: FPGA MicroBlaze Implementation

Update Contents: Chapters 4 and 5 have been updated.

Those who purchased the lecture, please download it from the data room.

In the future, the entire content of the "FPGA MicroBlaze Implementation" lecture will be continuously updated.

Thank you~!!

The lecture has been updated.

FPGA Utilization with Verilog (v2.1)

NRZL Decoder implementation (ch11) has been added.

Important information about implementing and using FIFO.

I hope it will be of great help in my practice.

FPGA Utilization for Zynq with Verilog (v1.2)

NRZL Decoder implementation (ch14) has been added.

Important information about implementing and using FIFO.

I hope it will be of great help in my practice.

Those who purchased the course can download it for free from the data room.

I hope this lecture will be of great help to you.thank you

hello.

[FPGA Utilization for Zynq using Verilog] lecture is now open.

This lecture is about adapting the contents of [FPGA Utilization using Verilog] to the Zynq mini 7020 (7010) board.

It has been newly organized.First half

vivado 2021.1 installation

Download the code implemented on the Zynq board and check the results

The second half

LED control using counter

SPI Controller

UART Controller

I2C Controller

Xilinx IP

To celebrate the opening of the course, we are offering a 30% discount.

Thank you for your interest.thank you

Verilog, FPGA lectures have been completed.

At first, I didn't think it would go this far,

Many people helped and responded

I think I was able to come this far.

I would like to express my sincere gratitude to everyone who has shown interest in my lectures.Let me briefly explain some tips for using the lecture.

1. Please familiarize yourself with the basic Verilog grammar before attending the lecture.

The lecture does not explain grammar. The lecture proceeds assuming that you know basic grammar. You only need to know basic grammar (reg, wire, always, module, etc.)2. Please start with “FPGA Utilization using Verilog”.

There is a lot of content included in this lecture.

Please read it carefully 2-3 times, implement it yourself with code, verify it with simulation, and upload it to the board to check.

If you want to learn verilog and fpga, learning by sight is of no use.

I have 25 years of total development experience, and about 20 years in the Verilog and FPGA fields.

Even now, to implement an i2c controller, you have to go through the process of coding and simulation verification dozens of times.

Lecture introduction: https://cafe.naver.com/worshippt/2663. Please use the “Basics of FPGA Utilization using Verilog” section as an appendix.

It consists of content that you should know at least once.

This lecture will be updated with additional content in the future.

Lecture introduction: https://cafe.naver.com/worshippt/2654. The FPGA MCU porting lecture is a course that can upgrade developers' skills to the next level.

I have applied the content of this lecture to numerous projects.

It is also used for debugging logic and is a very useful solution that does not require a separate MCU to be used externally.

In addition, you can freely utilize the memories inside the FPGA.

Lecture introduction: https://cafe.naver.com/worshippt/2685. If you properly understand the contents of the two MicroBlaze lectures, you can learn almost all the contents and apply them to your projects.

MicroBlaze offers great performance compared to MCU porting.

On the other hand, there are some limitations in configuring and applying memory.

If you know both MCU porting and MicroBlaze, you can choose which one to use depending on your project.

If you want something lightweight, you can use MCU porting, and if you need something high-performance, you can use MicroBlaze.

Lecture Introduction-1: https://cafe.naver.com/worshippt/269

Lecture Introduction-2: https://cafe.naver.com/worshippt/2706. DDR Controller lecture is a lecture required for fields that process Image Data.

To process image data, a Frame Buffer is required, and most Frame Buffers use DDR Memory.

This lecture explains everything from creating a DDR Controller to implementing a Framer Buffer.

Lecture introduction: https://cafe.naver.com/worshippt/267We will come back with better content in the future.

I would like to thank everyone again for their interest in my lecture.thank you