인프런 워밍업 클럽 스터디 4기 - CS 전공지식 > 2주차 발자국

◼만들면서 쉽게 배우는 컴퓨터 구조

Section5) 컴퓨터의 기초가 되는 하드웨어 만들기

MUX (Multiplexer, 멀티플렉서)

여러 입력 중 하나를 선택하여 출력으로 내보내는 장치

데이터 선택기라고도 불림

1비트 2입력 MUX

Selection 입력 값에 따라 A입력 또는 B입력을 선택하여 출력

Selection이 0 → 입력 A 선택

Selection이 1 → 입력 B 선택

8비트 4입력 MUX

4개의 8비트 입력 중 하나를 선택하여 출력

2비트의 Selection 입력 사용 (00₂ ~ 11₂)

00₂(0) → IN_0 출력

01₂(1) → IN_1 출력

10₂(2) → IN_2 출력

11₂(3) → IN_3 출력

8비트 8입력 MUX

8개의 8비트 입력 중 하나를 선택하여 출력

3비트의 Selection 입력 사용 (000₂ ~ 111₂)

000₂(0) → IN_0 출력

001₂(1) → IN_1 출력

010₂(2) → IN_2 출력

011₂(3) → IN_3 출력

100₂(4) → IN_4 출력

101₂(5) → IN_5 출력

110₂(6) → IN_6 출력

111₂(7) → IN_7 출력

디코더 (Decoder)

n비트 입력을 받아 2ⁿ개의 출력 중 하나만 활성화 시키는 장치

Enable 입력을 통해 디코더 회로 전체의 작동 여부를 제어

Enable이 0이면 모든 출력은 0 (비활성화 상태)

Enable이 1일 때에는 입력값에 따라 하나의 출력을 활성화

4비트 디코더 (Decoder)

4비트 입력 → 2^4 = 16개 출력 중 하나만 활성화

RAM 구현시 활용

컨트롤 버퍼

제어 신호에 따라 데이터를 흐르게 하거나 차단하는 버퍼

Section6) CPU 만들기: 산술논리연산장치 (ALU)

폰 노이만 구조 컴퓨터

입출력 장치 (I/O Device)

중앙 처리 장치 (CPU)

제어 유닛 (Control Unit)

산술 논리 연산 장치 (ALU)

메모리 (RAM)

→ 위 세 가지 구성 요소로 컴퓨터가 구성됨

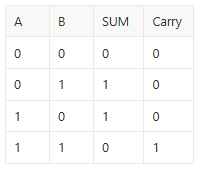

반가산기 (Half Adder)

두 개의 1비트 입력을 더하여, 합(Sum)과 자리올림(Carry)을 계산하는 조합 논리 회로

특징

입력: A, B (1비트씩)

출력: Sum[XOR로 구현], Carry[AND로 구현] (각 1비트)

자리올림(Carry-In)을 처리하지 못함 → 이전 자리의 올림을 고려하지 않음 → '반쪽짜리 가산기’ (반가산기)라 불림

진리표

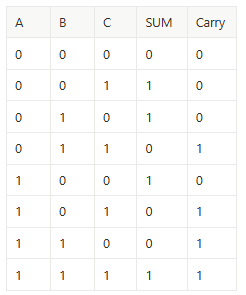

전가산기 (Full Adder)

세 개의 1비트 입력(두 입력 + 이전 자리의 자리올림)을 더하여, 합(Sum)과 자리올림(Carry-Out)을 계산하는 조합 논리 회로.

특징:

입력: A, B, Carry-In (1비트씩)

출력: Sum[반가산기 2개로 구현], Carry-Out[반가산기 2개+OR로 구현] (각 1비트)

자리올림을 연속적으로 처리 가능

진리표

산술 논리 연산 장치 (ALU: Arithmetic Logic Unit)

컴퓨터의 핵심 연산 장치로, 산술 연산과 논리 연산을 수행한다.

산술 연산 : 덧셈, 뺄셈, 증가, 감소, 곱셈, 나눗셈

논리 연산 : AND, OR, NOT, XOR, NAND, NOR 등

비교 연산 : ==, >, <, >=, <=

CPU 내부에 포함되어 있으며, 프로세서가 수행하는 계산의 대부분은 이 ALU를 통해 처리

음수 표현시 2의 보수 사용

Section7) 메모리 만들기

조합 논리 회로 (Combinational Logic Circuit)

출력이 현재 입력에만 의존하는 회로

상태를 기억하지 않음 (메모리 없음)

예시: AND, OR, NOT, Half Adder, Full Adder, Multiplexer, Decoder, ALU

순차 논리 회로 (Sequential Logic Circuit)

이전 입력에 대한 출력이 다시 입력으로 들어가는 회로

이전 상태를 기억

예시: SR Latch, D Latch, JK Latch, Flip-Flop, Register, RAM

SR Latch

Set(S)과 Reset(R) 입력을 갖는 기본 기억 회로

특정 조건에서 출력 Q는 이전 상태를 유지

Gated SR Latch는 Enable 신호가 1일 때만 동작

D Latch

S, R을 하나의 입력 D로 통합한 형태

Enable이 1일 때 D의 값을 Q에 저장

JK Latch

SR Latch의 단점 (S=R=1일 때 불안정)을 개선

J = Set, K = Reset 의미

J=K=1이면 출력이 반전 (Toggle 동작)

내부 딜레이가 있어 안정적인 동작 위해 Clock 필요

클럭과 플립플롭

Clock : enable을 0과 1로 반복해서 바꿔주는 신호 (Hz 단위로 동작)

Trigger

클럭 신호 중에서 "입력을 출력으로 반영하는 순간"을 결정하는 방식

종류

Level Trigger: High/Low 상태에서 작동 → D Latch

Edge Trigger: Rising/Falling 순간에 작동 → Flip-Flop

레지스터

8비트 저장 장치

여러 개의 Latch 또는 Flip-Flop으로 구성

Latch 또는 Flip-Flop : 1비트 저장장치

RAM (Random Access Memory)

주소를 통해 원하는 데이터에 접근 가능한 메모리

실행 중의 데이터와 상태를 임시로 저장

Mission2)

◼ 그림으로 쉽게 배우는 자료구조와 알고리즘

Section5) Red-Black 트리

Red-Black 트리

이진 탐색 트리의 일종으로,

데이터가 삽입되거나 삭제될때 트리의 균형을 자동으로 유지하는 균형 이진트리이다.

트리의 높이를 제한해 모든 연산의 최악의 시간복잡도를 O(log n)으로 유지하는 것이 목적

조건

모든 노드는 빨간색 혹은 검정색

루트 노드는 검은색

모든 리프 노드는 검은색

빨간색 노드의 자식은 검은색

모든 리프 노드에서 Black Depth는 같다

Section6) 우선순위 큐와 힙

우선순위 큐

데이터의 삽입 순서와는 상관 없이 우선순위가 높은 데이터가 먼저 나오는 큐

힙

완전 이진 트리 형태의 자료구조로, 부모 노드가 자식보다 크면 최대 힙, 작으면 최소 힙을 의미

🗒회고

MUX, 반가산기, 전가산기, 디코더, ALU 등 조합 논리 회로를 직접 구현해보며 각 장치의 동작 원리와 회로 구성 방식을 직관적으로 이해할 수 있었다.

또한 Register와 RAM 같은 순차 논리 회로를 만들며, 클럭과 Enable, 기억 소자의 역할, 메모리 동작 방식도 자연스럽게 배울수 있었다.

단순 이론을 넘어서 실제 회로 구조를 만들어 시각화 해보는 경험을 통해 컴퓨터 구조애 대한 이해력이 높아지고 있는것 같다.

🏷출처